Received 22 June 2017; accepted 28 July 2017. Date of publication 11 August 2017; date of current version 23 August 2017. The review of this paper was arranged by Editor A. Nathan.

Digital Object Identifier 10.1109/JEDS.2017.2737778

# First Demonstration of a Two-Tier Pixelated Avalanche Sensor for Charged Particle Detection

LUCIO PANCHERI<sup>1,2</sup> (Member, IEEE), ANDREA FICORELLA<sup>1,2</sup>, PAOLO BROGI<sup>3,4</sup>, G. COLLAZUOL<sup>5,6</sup>, GIAN-FRANCO DALLA BETTA<sup>1,2</sup> (Senior Member, IEEE), P. S. MARROCCHESI<sup>3,4</sup>, FABIO MORSANI<sup>4</sup>, LODOVICO RATTI<sup>7,8</sup> (Senior Member, IEEE), AURORE SAVOY-NAVARRO<sup>4,9</sup>, AND ARTA SULAJ<sup>3,4</sup>

1 Dipartimento di Ingegneria Industriale, Università di Trento, 38123 Trento, Italy 2 TIFPA INFN, 38123 Trento, Italy 3 DFSTA, Università di Siena, 53100 Siena, Italy 4 INFN Pisa, 56127 Pisa, Italy 5 Dipartimento di Fisica e Astronomia, Università di Padova, 35131 Padova, Italy 6 INFN Padova, 35131 Padova, Italy 7 Dipartimento di Ingegneria Industriale e dell'Informazione, Università di Pavia, 27100 Pavia, Italy 8 INFN Pavia, 27100 Pavia, Italy 9 Laboratoire APC, University Paris-Diderot/CNRS, 75013 Paris, France CORRESPONDING AUTHOR: L. PANCHERI (e-mail: lucio.pancheri@unitn.it) This work was supported by the APiX2 Experiment by Istituto Nazionale di Fisica Nucleare, CSN5.

**ABSTRACT** This paper presents the first experimental demonstration of a pixelated two-layer Geiger-mode avalanche sensor designed for the direct detection of charged particles. In the proposed device, each pixel is formed by two vertically aligned avalanche detectors, exploiting the coincidence between two simultaneous avalanche events to discriminate between the detection of particles and dark counts. A 48 × 16 pixel array has been designed and fabricated in a 150-nm CMOS process and vertically integrated through bump bonding. The pixel, that includes passive quenching, comparator, and digital electronic circuits for coincidence processing and signal storage, has a size of 50  $\mu$ m × 75  $\mu$ m and a maximum fill factor of 51.6%. The operation of the particle sensor has been validated with the measurement of dark count rate distribution at different coincidence resolution times. An average dark count rate per pixel as low as 93 mHz, corresponding to 24 Hz/mm<sup>2</sup>, was obtained at room temperature. A first sensor validation using a <sup>90</sup>Sr  $\beta$  source is presented.

**INDEX TERMS** Avalanche pixel sensor, particle detector, SPAD, CMOS, bump bonding.

## I. INTRODUCTION

In the last decade, CMOS technologies have proved to be excellent platforms for the realization of integrated optical sensors as well as for pixelated charged particle sensors [1]–[4]. While pinned photodiodes have become the detectors of choice in image sensors, the ultimate performance in terms of sensitivity and timing resolution for the detection of ultrafast optical signals can be obtained using Geiger-mode avalanche diodes, a.k.a. Single Photon Avalanche Diodes (SPADs) [5]. Pixelated CMOS optical sensors based on SPADs have been demonstrated in several application domains: among others it is worth mentioning optical ranging, Fluorescence Lifetime Imaging, Positron Emission Tomography and Raman Spectroscopy [6]–[11].

A preliminary study for the integration of a Geigermode avalanche particle detector in CMOS has also been presented [12]–[14]. Since in Geiger mode it is impossible to discriminate particle-generated signals from dark events, the use of two Geiger-mode avalanche diodes in coincidence has been proposed [15], but a pixel array based on this concept has never been presented so far. An experimental validation of the idea was carried out using two silicon photomultipliers (SiPM) in coincidence, demonstrating a detection efficiency larger than the SiPM geometrical Fill Factor, but without providing spatial information [16], [17].

In charged particle tracking and counting applications, the detectors of choice can be either hybrid or monolithic depending on the required resolution and radiation damage tolerance. In the case of hybrid detectors, bump bonding is typically used to connect the sensor array to a readout electronic chip. This approach offers the flexibility of customizing sensors and electronics independently, at the expense of a larger parasitic input capacitance. Since the input noise of the readout electronics is increased by large input capacitances, a large charge discrimination threshold needs to be set in hybrid detectors, thus limiting the minimum detectable charge. The large threshold affects the minimum detector thickness, that is around  $100\mu m$  in the hybrid pixels currently under development for tracking in high-energy physics applications [18], [19]. In State-of-the-Art monolithic detectors, the active area is typically limited to a few 10s of  $\mu m$  and full substrate depletion is not achieved. However, they exhibit a good signal-to-noise ratio thanks to their low parasitic capacitance, and their charge collection time can be as low as a few tens of ns [20]. For ultrafast timing applications, a class of detectors with low-gain avalanche amplification is emerging, providing a timing resolution as low as a few 10s of ps [21]. For this class of detectors, however, a fine pixelation has still to be demonstrated. If compared to existing solutions, the proposed Geiger-mode avalanche pixel is potentially interesting for combining fine pixelation, low material budget, low power consumption and timing resolutions that in principle can be lower than 100ps thanks to Geiger-mode operation.

To fully exploit the potential of the coincidence detection concept, low-noise avalanche detectors need to be co-integrated with deep submicron readout circuits, and two detector layers should be vertically integrated. Several examples of 3D-integrated SPAD arrays for optical sensing have been recently presented [22]–[24], supporting the technological feasibility of the proposed approach.

In this work, we present a two-layer sensor based on avalanche detectors in coincidence fabricated in a commercial 150nm CMOS process and integrated using a standard bump bonding technology. The architecture of the sensor is described in Section II. A selection of results from the experimental validation of the sensor is shown in Section III, while possible improvements of the proposed sensor in view of the potential applications are discussed in Section IV.

## **II. SENSOR DESIGN**

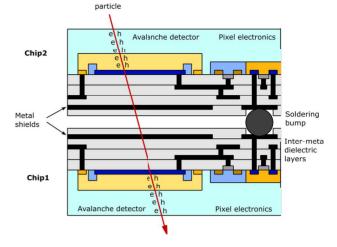

The coincidence pixel is composed of 2 levels of detectors and electronics, with a vertical interconnection used to deliver the digitized signal from the top to the bottom layer (Fig. 1).

The Geiger-mode detectors used in this work, fabricated in a commercial 150nm CMOS process (6 metal, 1 poly), have been previously developed for optical sensing applications [25], [26]. The detector junction, implemented as p+ or

FIGURE 1. Cross section of a two-layer CMOS pixel based on avalanche detectors in coincidence.

pwell in a deep nwell, is isolated from the p-type substrate. Therefore, the thickness of the active volume is very narrow, in the order of  $1\mu$ m [26]. The detectors have been covered with a metal shield to avoid optical cross-talk between different layers, but a few pixels have been left unshielded to enable optical tests.

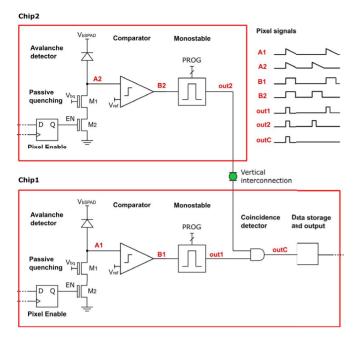

A simplified schematic diagram of the pixel is presented in Fig. 2. The detector front-end is the same in both layers, and includes a quenching transistor, a comparator and a programmable monostable for pulse shortening. The coincidence resolution time depends on the monostable pulse width, that can be set to three different nominal values of 750ps, 1.5ns or 10ns. A configuration register is used to independently enable or disable the pixels with an arbitrary pattern. The bottom half-pixel also includes a coincidence detector and digital electronic circuits for data storage (1bit/pixel) and readout.

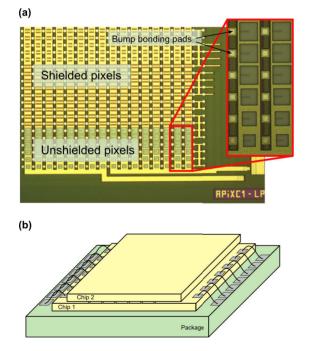

The pixel array, having a total size of  $16 \times 48$  pixels, is partitioned in subarrays with 4 different detector sizes. Each pixel has a size of 50  $\mu$ m x 75  $\mu$ m, with a maximum geometrical fill factor of 51.6%. The peripheral electronic circuits offer the flexibility for mapping dark count rate (DCR), timing resolution and crosstalk probability between different pixels in the same layer [27].

A micrograph of the bottom chip is shown in Fig. 3(a), while 3(b) shows a concept view of the complete sensor, where the two tiers have been vertically integrated using a flip chip process with SnAg solder bumps. In the final assembly, the bottom chip is connected to the package through standard wire bonds, while power, analog and digital signals are supplied from the bottom to the top chip through bump bonding pads.

### **III. EXPERIMENTAL RESULTS**

A few samples of top and bottom chips were wire-bonded for testing before proceeding to vertical integration. Electrical tests showed the correct functionality of both avalanche detectors and electronics in the two chips.

FIGURE 2. Simplified schematic of the pixel and illustration of pixel signals timing.

FIGURE 3. (a) Micrograph of the bottom chip (partial view) with detail of a group of pixel (b) Concept view of the vertically-integrated sensor assembly.

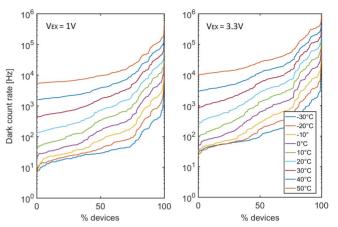

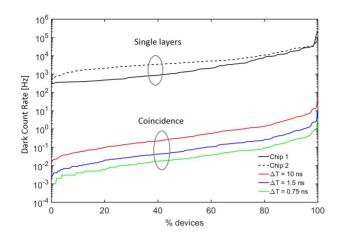

The measurements reported hereafter were conducted on detectors with an active junction of type pwell/deep nwell (indicated as Type 2 in [27]). The DCR cumulative distribution measured at different temperatures for two different excess voltages is shown in Figure 4 for the largest detectors, having 43  $\mu$ m × 45  $\mu$ m active area. A median DCR of 3 kHz, corresponding to 1.5 Hz/ $\mu$ m<sup>2</sup> was measured at

FIGURE 4. Pixel DCR distribution for 43  $\mu$ m × 45  $\mu$ m active area at two different excess bias voltages and at different temperatures.

room temperature and 3.3V overvoltage. It is worth noting that, for the best devices in the low part of the distribution, a DCR 10 times lower than the median value was measured. It can also be observed that, for these low-DCR devices, the DCR temperature coefficient tends to become very low at temperatures lower than  $-10^{\circ}$ C, indicating a generation rate dominated by band-to-band tunneling.

At room temperature, the DCR distribution is spread over more than two orders of magnitude. Analyzing the activation energy of the DCR time dependence, we found out that in most devices its value is lower than silicon  $E_G/2$ , indicating that the origin of DCR at room temperature is mainly due to trap-assisted tunnelling [27]. The large spread in the measured DCR can be explained considering that the shape of the DCR distribution is affected by the distribution of trapping centers inside the non-uniform electric field of the space-charge region. A similar distribution can be found in other SPAD-related works [5], [6].

Cross-talk measurements were also conducted at different voltages, demonstrating an average optical cross-talk in the range of a few percent between neighboring pixels at 3V overvoltage [28]. Preliminary single-photon timing resolution measurements, performed on unshielded samples with a blue picosecond laser, showed a timing resolution in the order of 200ps FWHM, even though the array electronics was not optimized for timing. The core of each chip, working at 1.8V, absorbs a current of 8mA, mainly due to the static current required by the comparators. A summary of the electrical tests performed on the single chips before vertical integration is presented in [27] and [28].

In the vertically integrated assemblies, the functionality of both layers was preserved after bump bonding, even though a small number of pixels was not working in the bottom chip. The measurements presented hereafter were conducted on a  $8 \times 24$  subarray, where all the pixels have the same detector type and size and are all functional. Also in this case, the detectors active area is 43  $\mu$ m × 45  $\mu$ m and the pixels have 51.6% Fill Factor. The DCR could be mapped correctly on

**FIGURE 5.** DCR distribution of the pixels measured separately in the two chips and distribution of the DCR in coincidence for 3 different settings of the pixel monostable circuit. Measurements are done at T=20°C and  $V_{EX} = 1$  V.

both layers and was in agreement with previous measurements. The distribution of dark coincidence measurements in the array, with the 3 different monostable width settings, are shown in Figure 5 together with the DCR of the separate layers. The average coincidence DCR ( $DCR_C$ ) is as low as 93 mHz per pixel with the minimum pulse width, corresponding to 24 Hz/mm<sup>2</sup>. This value is in good agreement with the theoretical value predicted by

$$DCR_C = DCR_1 \cdot DCR_2 \cdot 2\Delta T \tag{1}$$

where  $DCR_1$  and  $DCR_2$  is the DCR of the two layers, separately, and  $\Delta T$  is the coincidence resolution time defined by the monostable pulse width.

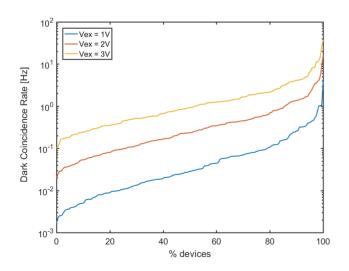

**FIGURE 6.** DCR distribution of the pixels as a function of  $V_{EX}$ . Measurements are done at T=20°C and  $\Delta T$  = 0.75 ns.

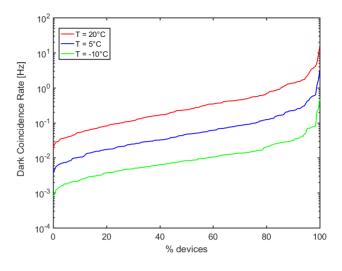

The coincidence DCR distribution is shown as a function of  $V_{EX}$  and temperature in Figures 6 and 7. It is worth noting that both the voltage and temperature dependence of DCR

**FIGURE 7.** DCR distribution of the pixels as a function of temperature. Measurements are done at  $V_{EX} = 2 V$  and  $\Delta T = 0.75$  ns.

is enhanced by the coincidence, since they affect both terms  $DCR_1$  and  $DCR_2$  in equation 1.

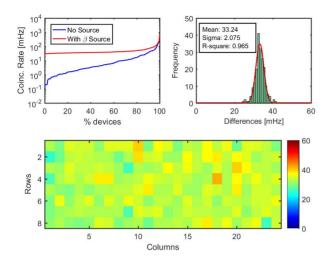

A validation of the sensor operation with charged particles was carried out using a  ${}^{90}$ Sr  $\beta$  source with 39 kBq±6% activity and 2 cm<sup>2</sup> area. The source was placed on top of the sensor at 5 mm distance from its surface. The setup was placed in a climate chamber and cooled to  $5^{\circ}$ C, in order to reduce the DCR to levels comparable or lower than the count rate induced by the  $\beta$  source, and the sensors were biased with  $V_{EX} = 1V$ . In the measurements, a large number of frames with 1 ms integration time were summed, to obtain a total accumulation time of 10000 s. The count rate distribution was acquired both in the presence and in the absence of the source, and is shown in Figure 8(a), while the distribution of the count rate difference is shown in Figure 8(b). Figure 8(c) shows a response map of the array, that does not exhibit any apparent gradient. This is not surprising, since the source size is much larger than the detector and was centered on it for the measurements.

The average count rate per pixel induced by  $\beta$  particles is approximately 33mHz, while the distribution follows the Poisson statistics. Since the total measurement time was  $10^4$  s, considering only the beta events, the expected uncertainty due to Poisson statistics should be  $\sigma = \sqrt{0.033/10^4} =$ 1.8 mHz. The measured uncertainty is  $\sigma = 2$  mHz, in good agreement with the estimated value.

### **IV. DISCUSSION**

The measurements carried out with the beta source provide a first means to evaluate the performance of the sensor in particle counting applications. The measured count rate corresponds to a detection rate of 8.8 events/(mm<sup>2</sup>s), to be compared with  $197\pm6\%$  events/(mm<sup>2</sup>s) emitted by the  $^{90}$ Sr source. Monte Carlo (MC) simulations were used to quantify the different effects accounting for the observed charged-particle detection efficiency.

**FIGURE 8.** (a) Count rate distribution with and without  $\beta$  source. (b) Distribution of the count rate difference. (c) Map of the count rate difference.

Among the several factors accounting for the measured inefficiency, the most relevant one is the geometric acceptance of the detector, which depends on the relative position between source and detector. According to MC simulations, with the geometrical arrangement used in the measurements, the hit rate on the detector surface should amount to 50 Hz/mm<sup>2</sup>.

Another important contribution is given by the pixel fill factor, whose design value is around 50%. Previous measurement campaigns conducted on SiPMs suggest that the geometrical fill factor in the case of particles might be larger than the one measured optically [17], but this should be experimentally confirmed on this CMOS prototype using a controlled particle beam with nearly orthogonal incidence.

The thickness of the top chip is 280  $\mu$ m, so a consistent fraction of the low-energy particles emitted by the <sup>90</sup>Sr source is absorbed in the substrate of the top chip before arriving to the active region. According to MC simulations, only 40% of the  $\beta$  particles arriving at the surface can reach the active layer.

The angle of incidence constitutes another source of inefficiency, since particles hitting the sensor with a nonorthogonal angle might generate a signal only in one of the two layers. Particles incident at large angles are more likely to fail hitting both layers.

Some events, despite crossing the sensor within the active volume, might not generate charge due to the granularity of charge release in the very thin active region. MC simulations predict that, in more than 99% of the cases, at least 1 electron is released in the active volume, while at least 5 electrons are generated in 97.5% of cases.

Last, even if one or more electron-hole pairs are generated within the active volume, there might be a small chance that the avalanche is not self-sustaining since the avalanche triggering probability  $P_t$  is lower than 100%. The value of  $P_t$  due to charged particle could be estimated starting from optically measured data. If  $P_{t1}$  is the triggering probability associated with 1 generated electron-hole pair, i.e., the value measured optically, the combined triggering probability  $P_{tN}$ , due to the generation of N electron-hole pairs, can be estimated as

$$P_{tN} = 1 - (1 - P_{t1})^N.$$

(2)

If, for example,  $P_{t1} = 50\%$ , according to equation 2  $P_{t5} = 97\%$  and  $P_{t10} = 99.9\%$ . Therefore, even though the opticallymeasured avalanche triggering probability is far from 100%, in most cases several electrons are generated with charged particles and the combined probability can be very close to 100%.

Taking all these effects into account, MC simulations predict a particle-induced count rate of 7.3 Hz/mm<sup>2</sup>, in good agreement with the experimentally measured 8.8 Hz/mm<sup>2</sup> rate.

#### **V. CONCLUSION**

In this paper, we have presented the first demonstration of a pixel array for charged particles based on Geiger-mode avalanche detectors in coincidence. The experimental results indicate that detectors with a fine pixelation, a good uniformity and small power consumption are feasible with the adopted technology. The coincidence DCR depends on the DCR statistics of the single detectors, that in turn is strongly affected by the distribution of defects in the sensor active volume. MC analysis has showed that the main limitations to the detection efficiency are the thickness of the top-chip substrate and the geometrical fill factor of the detectors.

It is worth noting that the aforementioned factors can be addressed and both the sensor DCR and its particle detection efficiency can be improved. In fact, sensors based on the proposed concept can benefit from the technological developments of CMOS-integrated SPADs. The pixel DCR can be reduced by employing dedicated implantations and processes customized for image sensors [5], while the geometrical fill factor, not optimized in this first trial, can be increased by adopting a more scaled CMOS process [23]. With an advanced process node, the pixel size can also be reduced with a minimum loss of efficiency. Since the devices have a very small active thickness and are isolated from the substrate, the substrates can be thinned down to a few microns without compromising sensor functionality and DCR.

An aggressive thinning would enable the stacking of more than two layers for improved efficiency while maintaining a low material budget. These properties, together with the picosecond timing resolution achievable thanks to Geigermode operation, make the proposed sensors appealing for particle counting and timing in high-energy physics and medical applications.

## REFERENCES

E. R. Fossum and D. B. Hondongwa, "A review of the pinned photodiode for CCD and CMOS image sensors," *IEEE J. Electron Devices Soc.*, vol. 2, no. 3, pp. 33–43, May 2014, doi: 10.1109/JEDS.2014.2306412.

- [2] Y. Değerli *et al.*, "A digital monolithic active pixel sensor chip in a quadruple-well CIS process for tracking applications," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 5, pp. 3899–3906, Oct. 2013, doi: 10.1109/TNS.2013.2280794.

- [3] K. Hara *et al.*, "Development of FD-SOI monolithic pixel devices for high-energy charged particle detection," in *Proc. IEEE Nucl. Sci. Symp. Conf. Rec.*, Valencia, Spain, 2011, pp. 1045–1050, doi: 10.1109/NSSMIC.2011.6154318.

- [4] I. Perić, "A novel monolithic pixelated particle detector implemented in high-voltage CMOS technology," Nucl. Instrum. Methods Phys. Res. A Accelerators Spectrometers Detectors Assoc. Equipment, vol. 582, no. 3, pp. 876–885, 2007, doi: 10.1016/j.nima.2007.07.115.

- [5] M. Ghioni, A. Gulinatti, I. Rech, F. Zappa, and S. Cova, "Progress in silicon single-photon avalanche diodes," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. 4, pp. 852–862, Jul./Aug. 2007, doi: 10.1109/JSTQE.2007.902088.

- [6] E. Charbon, "Single-photon imaging in complementary metal oxide semiconductor processes," *Philosoph. Trans. Roy Soc. A*, vol. 372, no. 2012, 2014, Art. no. 20130100, doi: 10.1098/rsta.2013.0100.

- [7] D. Bronzi *et al.*, "Automotive three-dimensional vision through a single-photon counting SPAD camera," *IEEE Trans. Intell. Transp. Syst.*, vol. 17, no. 3, pp. 782–795, Mar. 2016, doi: 10.1109/TITS.2015.2482601.

- [8] C. Niclass, M. Soga, H. Matsubara, M. Ogawa, and M. Kagami, "A 0.18-μm CMOS SoC for a 100-m-range 10-frame/s 200 × 96pixel time-of-flight depth sensor," *IEEE J. Solid-State Circuits*, vol. 49, no. 1, pp. 315–330, Jan. 2014, doi: 10.1109/JSSC.2013.2284352.

- [9] M. Popleteeva *et al.*, "Fast and simple spectral FLIM for biochemical and medical imaging," *Opt. Exp.*, vol. 23, no. 18, pp. 23511–23525, 2015, doi: 10.1364/OE.23.023511.

- [10] L. H. C. Braga *et al.*, "A fully digital 8 × 16 SiPM array for PET applications with per-pixel TDCs and real-time energy output," *IEEE J. Solid-State Circuits*, vol. 49, no. 1, pp. 301–314, Jan. 2014, doi: 10.1109/JSSC.2013.2284351.

- [11] J. Kostamovaara *et al.*, "Fluorescence suppression in Raman spectroscopy using a time-gated CMOS SPAD," *Opt. Exp.*, vol. 21, no. 25, pp. 31632–31645, 2013, doi: 10.1364/OE.21.031632.

- [12] E. Vilella *et al.*, "A test beam setup for the characterization of the Geiger-mode avalanche photodiode technology for particle tracking," *Nucl. Instrum. Methods Phys. Res. A Accelerators Spectrometers Detectors Assoc. Equipment*, vol. 694, pp. 199–204, Dec. 2012, doi: 10.1016/j.nima.2012.08.026.

- [13] E. Vilella, O. Alonso, and A. Diéguez, "3D integration of Geiger-mode avalanche photodiodes aimed to very high fill-factor pixels for future linear colliders," *Nucl. Instrum. Methods Phys. Res. A Accelerators Spectrometers Detectors Assoc. Equipment*, vol. 731, pp. 103–108, Dec. 2013, doi: 10.1016/j.nima.2013.05.022.

- [14] E. Vilella, O. Alonso, A. Vilá, and A. Diéguez, "Strategies for using GAPDs as tracker detectors in future linear colliders," *Nucl. Particle Phys. Proc.*, vols. 273–275, pp. 1072–1078, Apr./Jun. 2016, doi: 10.1016/j.nuclphysbps.2015.09.168.

- [15] V. Saveliev, "Avalanche pixel sensors and related methods," U.S. Patent 8 269 181, Sep. 18, 2012.

- [16] N. D'Ascenzo et al., "Silicon avalanche pixel sensor for high precision tracking," J. Instrum., vol. 9, no. 3, Mar. 2014, Art. no. C03027.

- [17] P. S. Marrocchesi *et al.*, "Charged particle detection with NUV-sensitive SiPM in a beam of relativistic ions," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 5, pp. 2786–2793, Oct. 2014, doi: 10.1109/TNS.2014.2348794.

- [18] N. Savic et al., "Thin n-in-p planar pixel modules for the ATLAS upgrade at HL-LHC," Nucl. Instrum. Methods Phys. Res. A, vol. 845, no. 11, pp. 154–158, Feb. 2017, doi: 10.1016/j.nima.2016.05.113.

- [19] M. Meschini et al., "The INFN-FBK pixel R&D program for HL-LHC," Nucl. Instrum. Methods Phys. Res. A Accelerators Spectrometers Detectors Assoc. Equipment, vol. 831, pp. 116–121, Sep. 2016, doi:10.1016/j.nima.2016.05.009.

- [20] C. Riegel *et al.*, "Radiation hardness and timing studies of a monolithic TowerJazz pixel design for the new ATLAS inner tracker," *J. Instrum.*, vol. 12, no. 1, Jan. 2017, Art. no. C01015, doi:10.1088/1748-0221/12/01/C01015.

- [21] N. Cartiglia et al., "Design optimization of ultra-fast silicon detectors," Nucl. Instrum. Methods Phys. Res. A Accelerators Spectrometers Detectors Assoc. Equipment, vol. 796, pp. 141–148, Oct. 2015, doi: 10.1016/j.nima.2015.04.025.

- [22] B. F. Aull *et al.*, "A study of crosstalk in a 256 × 256 photon counting imager based on silicon Geiger-mode avalanche photodiodes," *IEEE Sensors J.*, vol. 15, no. 4, pp. 2123–2132, Apr. 2015, doi: 10.1109/JSEN.2014.2368456.

- [23] T. Al Abbas *et al.*, "Backside illuminated SPAD image sensor with 7.83μm pitch in 3D-stacked CMOS technology," in *Proc. IEDM*, San Francisco, CA, USA, 2016, pp. 8.1.1–8.1.4, doi: 10.1109/IEDM.2016.7838372.

- [24] J. M. Pavia, M. Scandini, S. Lindner, M. Wolf, and E. Charbon, "A 1 × 400 backside-illuminated SPAD sensor with 49.7 ps resolution, 30 pJ/Sample TDCs fabricated in 3D CMOS technology for nearinfrared optical tomography," *IEEE J. Solid-State Circuits*, vol. 50, no. 10, pp. 2406–2418, Oct. 2015, doi: 10.1109/JSSC.2015.2467170.

- [25] L. Pancheri and D. Stoppa, "Low-noise single photon avalanche diodes in 0.15 μm CMOS technology," in *Proc. Eur. Solid-State Device Res. Conf. (ESSDERC)*, Helsinki, Finland, 2011, pp. 179–182, doi: 10.1109/ESSDERC.2011.6044205.

- [26] L. Pancheri, D. Stoppa, and G.-F. Dalla Betta, "Characterization and modeling of breakdown probability in sub-micrometer CMOS SPADs," *IEEE J. Sel. Topics Quantum Electron.*, vol. 20, no. 6, pp. 328–335, Nov./Dec. 2014, doi: 10.1109/JSTQE.2014.2327791.

- [27] L. Pancheri et al., "First prototypes of two-tier avalanche pixel sensors for particle detection," Nucl. Instrum. Methods Phys. Res. A Accelerators Spectrometers Detectors Assoc. Equipment, vol. 845, pp. 143–146, Feb. 2017, doi: 10.1016/j.nima.2016.06.094.

- [28] A. Ficorella et al., "Crosstalk mapping in CMOS SPAD arrays," in Proc. 46th Eur. Solid-State Device Res. Conf. (ESSDERC), Lausanne, Switzerland, 2016, pp. 101–104, doi: 10.1109/ESSDERC.2016.7599598.

**LUCIO PANCHERI** (M'11) received the M.Sc. degree in materials engineering and the Ph.D. degree in information and communication technologies from the University of Trento, Italy, in 2002 and 2006, respectively. From 2006 to 2012, he has been a Research Scientist with Fondazione Bruno Kessler, Trento, Italy, where he has been involved in the development of CMOS optical sensors for advanced imaging and biomedical applications. From 2012, he is an Assistant Professor with the University of Trento. In the last years, his research activity has been mainly focused on the development of silicon sensors for optical, X-ray, and charged particle imaging. He has authored or co-authored over 100 papers in international journals and presentations at international conferences.

**ANDREA FICORELLA** received the master's degree in medical engineering from the University of Rome Tor Vergata, Italy, in 2014. He is currently pursuing the Ph.D. degree with the Industrial Engineering Department, University of Trento, Italy. His main research activities are semiconductor detector systems, fluorescence lifetime imaging, and nanodosimetry.

**PAOLO BROGI** was born in Siena, Italy, in 1986. He received the bachelor's degree in Fisica e Tecnologie Avanzate from the University of Siena, in 2005, the master's degree in physics (curriculum "Interazioni Fondamentali") from the University of Pisa, in 2011, and the Ph.D. degree in experimental physics from the University of Siena, in 2015. Since 2015, he has been a recipient of a research grant with the University of Siena. His current research work is in the framework of the study of high energy cosmic radiation with the CALET experiment on the ISS. His research and development of new detectors for particle identification and tracking.

**G. COLLAZUOL** photograph and biography not available at the time of publication.

**GIAN-FRANCO DALLA BETTA** (S'94–M'98–SM'06) was born in Venice, Italy, in 1967. He received the M.S. degree in electronics engineering from the University of Bologna, Bologna, Italy, in 1992 and the Ph.D. degree in microelectronics from the University of Trento, Trento, Italy, in 1997. From 1997 to 2002, he was with ITC-irst, Trento, Italy. Since 2002, he has been with the University of Trento, Trento, Italy. Since 2002, he has been with the University of Trento, Trento, Italy, where he is currently a Full Professor of electronics. He has authored or co-authored over 350 papers published in international journals and conference proceedings. His main research interests are in silicon radiation detectors and integrated optical sensors. He has been serving as an Associate Editor of the IEEE TRANSACTIONS ON NUCLEAR SCIENCE since 2008.

**P. S. MARROCCHESI**, photograph and biography not available at the time of publication.

**FABIO MORSANI** received the M.S. degree in physics and electronics designer from INFN-Pisa, Italy, where he has been a Coordinator of the Electronics Workshop, Since 1983. He collaborated to several high-energy physics experiments at CERN (NA31, Aleph, A48, CMS, Atlas), Fermilab (CDF), Stanford (BaBar), PSI (MEG), and to several research and development initiatives. His research interests are mainly in trigger and readout systems, VLSI full-custom chips, from first associative memory chip for CDF SVT to pixel array readout ICs, and in medical applications of silicon detectors.

**LODOVICO RATTI** (M'00–SM'13) received the M.S. degree in electronic engineering and the Ph.D. degree in electronic engineering and computer science from the University of Pavia, Italy, in 1996 and 2000, respectively, where he has been with an Associate Professor with the Department of Electrical, Computer and Biomedical Engineering, since 2014. He has authored over 130 papers published in peer-reviewed international journals and over 180 works presented at international conferences and workshops. His main research interests are in low-noise front-end for radiation detectors, monolithic pixel sensors, vertically integrated circuits, and noise and radiation tolerance characterization of microelectronic technologies, mostly CMOS.

**AURORE SAVOY-NAVARRO** a High Energy Physicist and the Director of Research with CNRS, France. She has participated in the main particle physics experiments with CERN and FNAL, USA, with discoveries, such as, W and Z0 (CERN), Top quark (FNAL), matter/antimatter oscillations (FNAL), and Higgs (CERN). She got several invited positions (CERN, USA) and as a PI of European networks. The contributions are on both detector design and construction (advanced detector technologies and microelectronics research and development for signal processing) and physics analyses. They imply training new generations of researchers in new physics exploration and close collaboration with engineers and high tech industry. The present focus is on new silicon pixels and associated intelligent fast signal processing including also high performance and real time computing, for the high luminosity LHC.

**ARTA SULAJ**, photograph and biography not available at the time of publication.