### Terahertz Detectors and Imaging Array with In-Pixel Low-Noise Amplification and Filtering in CMOS technologies

A PhD dissertation presented by

### **Muhammad Ali**

То

Integrated Radiation and Image Sensors (IRIS) Fondazione Bruno Kessler, Italy

&

Information and Communication Technology (ICT) University of Trento, Italy

Submitted in partial fulfilment for the degree of Doctor of Philosophy

PhD Supervisor:

Matteo Perenzoni (Senior Researcher) Fondazione Bruno Kessler, Italy

#### **Commission Members:**

Prof. Gianfranco Dalla Betta, Prof. Andrea Neviani, Prof. Alessandro Tredicucci

Trento, April 2017

## **Declaration**

I, Muhammad Ali, hereby declare that I wrote this thesis independently as part of the Doctoral work performed at Fondazione Bruno Kessler and University of Trento, Italy. I have clearly mentioned the aid, support and data taken from any external source.

Muhammad Ali

### Abstract

*Terahertz gap* corresponding to the frequency band of 0.3-3.0 THz is historically the last unexplored region of the electromagnetic spectrum left to be fully investigated. The major difficulty that has hampered the maturation of technologies operating in this region lies in the fact that much unlike its bordering millimeter and infrared regions, generation and detection of THz radiation is not trivial. Yet, such is the intriguing nature and properties of the terahertz radiations that the interest in this region has not faded. Infact, potential applications of THz based systems have emerged in various fields including biomedical imaging, safety and security, quality control and communication.

Over the past decade, a lot of research work has been published with an aim to bridge this *gap* by both electronics and photonics based systems. While these attempts have succeeded to a certain extent, the available solutions either lack in terms of performance or are mostly bulky and difficult to integrate for portable and commercial purpose.

This PhD dissertation focuses on the design and investigation of direct terahertz detectors which could be operated at room temperature and fabricated in standard silicon technologies, thereby making use of several advantages like high level of integration, low cost and small device size that these technologies have to offer. In particular, the emphasis is on developing and characterizing terahertz systems for imaging application by using field effect transistor devices as detectors. This objective is pursued in three parts.

The first part (chapter 3) of the dissertation deals with the measurement and characterization challenges of terahertz systems. Unlike guided mode solutions, measurements of terahertz detectors and their systems require free space which presents several challenges due to atmospheric attenuation, spurious reflections and diffractions, beam shaping, and so on. Moreover, background noise is also significant considering that the detected signal is typically in the order of a few microvolts. In this regard, an overview of the most common techniques is given and a measurement methodology involving the use of a reference pyroelectric detector to measure the impinging input power and techniques for the evaluation of the detector under-test effective area is presented.

The second part (chapter 4) is related to the investigation of variants of antennacoupled field effect transistor and schottky barrier diode in standard 180 nm CMOS process as examples of direct detectors. During laboratory characterization, detection of terahertz radiation from schottky diode could not be achieved due to matching issues. Moreover, optimization of schottky diode by modifying its standard cell proved to be challenging as compared to field effect transistor, which can be optimized easily to enhance performance parameters and was therefore finally chosen as the preferred choice.

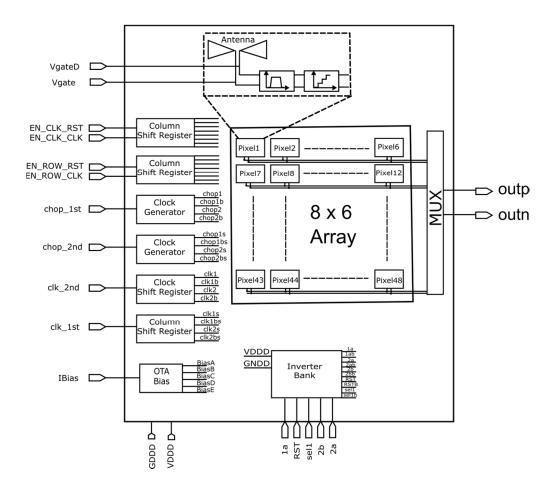

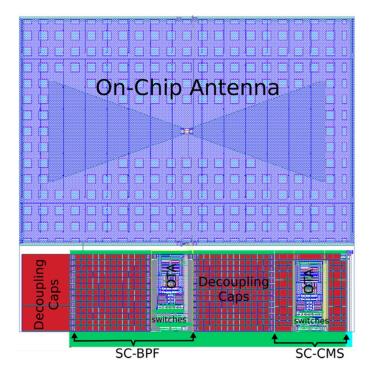

The final part of the thesis (chapters 5 and 6) concerns with the implementation of analog readout interface to perform signal processing of detected terahertz signal. First, a single pixel consisting of on-chip antenna-coupled detector and a switched capacitor based filtering operation is designed and fabricated in 0.15µm process. The pixel is tested by performing both electrical and terahertz characterization, achieving high voltage responsivity value of 470 kV/W and a minimum NEP of 480 pW/sqrt (Hz). The interface architecture is highly repeatable and it can be used with any commercially terahertz source, even if its operation is limited by low modulation frequency. On the basis of the successful measurement results, an 8 x 6 terahertz array for real-time imaging application is fabricated in the same technology by modifying the interface architecture to make it power and area efficient.

# **Thesis: Objective and Contributions**

The objective of this thesis is to investigate Silicon based direct THz detectors and systems for imaging applications implemented in standard CMOS technologies with a special emphasis on Field Effect Transistor (FET)-based detectors. This thesis involves design, fabrication and characterization of various chips and I had been involved in carrying out most of these tasks. A brief overview of the chapter contents is given below.

#### Chapter 1 Introduction

This chapter presents an overview of the state-of-the-art THz devices, sources and detectors with an emphasis on their utilization in various applications. The merits and demerits of these devices are discussed and summarized in tabular forms along with their most important performance parameters. THz region is explained with reference to the electromagnetic spectrum: its fascinating properties and the potential applications of THz based systems is outlined.

#### Chapter 2 Theory of CMOS based FET THz detection

The advantages of fabricating THz detectors in standard CMOS technologies are presented here. The chapter then discusses the underlying theory of the plasma waves generation in the FET channel in the historical context. Moreover, the quasi static and Non-Quasi static modeling shows the rectification of the incoming THz signal of the FET channel.

#### Chapter 3 Measurement techniques for direct THz detectors

This part deals with the investigation of various laboratory techniques for the realtime measurement and characterization of direct THz detectors. In particular, accurate measurements regarding the impinging input power received by the detector and its effective area illuminated by THz radiation are important as they directly affect the performance parameters. An overview of existing methods and their limitations are discussed. Moreover, a methodology involving the use of a reference pyroelectric detector to accurately measure the input power is presented. This methodology is validated on a test structure consisting of an on-chip antenna and a FET based direct THz detector implemented in a standard 0.18µm technology.

#### Chapter 4 Simulation and Optimization of FET THz detectors

In this chapter the performance parameters of direct THz detector are defined. The results from SPICE simulation of FET detector are compared with the theoretical/mathematical modeling describing the performance parameters. Moreover several variants of the FET detector, based on the difference in configuration and device parameters are characterized using the test methodology of Chapter 3.

# Chapter 5 Single-pixel design and readout interface for FET THz detector

This chapter discusses the theoretical details and simulations of the Switched Capacitor readout interface to process the detected signal of the FET THz detector are presented. The focus has been to design a low noise, robust and repeatable interface that could achieve high voltage responsivity and preserve the detector NEP. The electrical and THz characterization results are presented, confirming the functionality of pixel.

#### Chapter 6 Terahertz imaging array

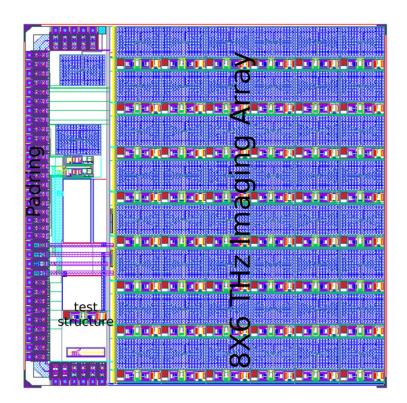

The chapter presents an improved readout interface architecture for a FET detector, which is different from the one presented in Chapter 5. The main objective of designing a new architecture is to reduce power consumption and pixel area as compared to the previous pixel. Based on this interface, an 8 x 6 THz imaging array has been fabricated. The theoretical design details, simulations and characterization results are presented in this chapter.

#### Chapter 7 Thesis conclusion and Future prospects

## **List of Publications**

#### Journal Article(s)

<u>M. Ali</u>, M. Perenzoni and D. Stoppa, "A Methodology to Measure Input Power and Effective Area for Characterization of Direct THz Detectors," in *IEEE Transactions on Instrumentation and Measurement*, vol. 65, no. 5, pp. 1225-1231, May 2016.

#### **Conference Publications**

- M. Zanoli, <u>M. Ali</u> and M. Perenzoni, "A 8-6 pixel THz Focal Plane Array with Per-Pixel High-Gain Readout Channel in 150 nm CMOS Technology," 42nd International Conference on Infrared, Millimeter, and Terahertz waves (IRMMW-THz), 2017 (submitted).

- <u>M. Ali</u>, M. Perenzoni and D. Stoppa, "A high-gain, low-noise switched capacitor readout for FET-based THz detectors," *42nd European Solid-State Circuits Conference*, Lausanne, Switzerland, 2016, pp. 401-404.

- <u>M. Ali</u>, M. Perenzoni and D. Stoppa, "A measurement setup for THz detectors characterization validated on FET-based CMOS test structures," *IEEE International Instrumentation and Measurement Technology Conference (I2MTC) Proceedings*, Pisa, 2015, pp. 320-324.

- <u>M. Ali</u> and M. Perenzoni, "Comparison of gate driven and source driven FET structures as THz detectors," *Proc. SPIE*, vol. 9141, pp. 914106-1–914106-9, May 2014.

### Keywords

CMOS, Terahertz, imaging, Field Effect Transistors, modulation, direct detectors, Noise Equivalent Power (NEP), voltage and current Responsivity (R), readout interface, Switched Capacitor (SC) filters, antenna gain, directivity, polarization, thermal noise, flicker noise, chopper stabilized circuit, gm/id design, deice optimization, real time imaging, focal plane array, correlated multiple sampling, non-linear device, solid state, antenna-coupled

### Acknowledgements

I would like to express my gratitude to my advisor Mr. Matteo Perenzoni and group head Dr. David Stoppa for providing me an opportunity to work on this dissertation in Integrated Radiation and Image Sensor (IRIS) group, Fondazione Bruno Kessler (FBK) Italy. I am indebted to Matteo's valuable guidance throughout this work and the efforts he had put in to review this thesis. I would also like to thank other members of IRIS including Dr. Leonardo Gasparini, Nicola Massari and Massimo Gottardi, as well as Dr. Lucio Pancheri of the University of Trento. My special appreciation goes to Daniele Perenzoni and Daniele Rucatti for helping me out in various laboratory and chip measurement activities and for useful technical discussion.

I would like to thank current and former PhD students I had the pleasure of working with, including Olufemi Olumodeji, Hesong Xu, Leo Huf Campos Braga and Moustafa Khatib. My special appreciation goes to Suzana Domingues for regularly helping me out and our several useful discussions regarding technical contents of the topic. I would also like to thank Marco Zanoli for carrying out measurements of 3<sup>rd</sup> chip.

My friends in Trento proved a great source of fun and happiness which made my stay in Italy very memorable. I would like to thank Usman Raza for our long chats and for the help he provided me on various matters in the initial stages of my PhD. Maqsood Ahmed, Musawar Saeed, and Atta *Bhai:* you guys had been wonderful in arranging parties in San Bartolomeo.

My dearest friend Usman Hafeez Sandhu: I know I have found a gem of a person in you. I would like to thank you and your family for hosting countless dinners and for making us laugh with your light banter.

I extend my gratitude to Mr. Harald Neubauer for giving me an opportunity to work in the Fraunhofer Institute of Integrated Circuits (IIS), Germany after I finished the technical work at FBK. My appreciation also goes to other colleagues including Dr. Stephan Junger and Thomas Schweiger. In particular I would like to thank Dr. Matthias Oberst for his patience and guidance regarding my work in IIS.

I would like to thank my wife *Ameera* for standing by my side through every thick and thin and for helping me out to get through difficult times. It was her love, insistence and motivation that kept me going even in those moments when a part of me thought of giving up. Our bond strengthened during this time and also with the arrival of our son *Azlaan* who filled our lives with joy and happiness.

And finally above all, I owe my every success and specially this one to my mother for all the sacrifices she had made in her life just so I could have my dreams fulfilled. I thank you for filling me with determination, passion and hunger to achieve my goals and for believing in me. I know how much this means to you. To my family

### List of Symbols, Abbreviations and Glossary

| EM   | Electromagnetic                         |

|------|-----------------------------------------|

| IR   | Infrared                                |

| THz  | Terahertz                               |

| Si   | Silicon                                 |

| eV   | Electron volt                           |

| К    | Kelvin                                  |

| W    | Watt                                    |

| SOA  | State of the Art                        |

| FEL  | Free Electron Laser                     |

| CMOS | Complementary Metal Oxide Semiconductor |

| QCL  | Quantum Cascade Laser                   |

| IF   | Intermediate Frequency                  |

| LO   | Local Oscillator                        |

| PA   | Power Amplifier                         |

| QS   | Quasi Static                            |

| NQS  | Non Quasi Static                        |

| KCL  | Kirchhoff Current Law                   |

| PDE  | Partial Differential Equation           |

| KVL  | Kirchhoff Voltage Law                   |

| GD   | Gate Driven                             |

| SD   | Source Driven                           |

| DR   | Dynamic Range                           |

| MDS  | Minimum Detectable Signal               |

| NEP  | Noise Equivalent Power                  |

| VCVS | Voltage Controlled Voltage Source       |

| OPAMPOperational AmplifierS&HSample and HoldFOMFigure of MeritGBWGain BandwidthBWBandwidthAMAmplitude ModulationDDirectivityFPAFocal Plane ArrayDUTDevice under TestBNBackground NoiseUCAUser Controlled AttenuationSCSwitched CapacitorFETField Effect TransistorSBDSchottky Barrier DiodeSNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterQFQuality Factor                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FOMFigure of MeritGBWGain BandwidthBWBandwidthBWBandwidthAMAmplitude ModulationDDirectivityFPAFocal Plane ArrayDUTDevice under TestBNBackground NoiseUCAUser Controlled AttenuationADCAnalog to Digital ConverterSCSwitched CapacitorFETField Effect TransistorSBDSchottky Barrier DiodeSNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor |

| GBWGain BandwidthBWBandwidthAMAmplitude ModulationAMAmplitude ModulationDDirectivityFPAFocal Plane ArrayDUTDevice under TestBNBackground NoiseUCAUser Controlled AttenuationADCAnalog to Digital ConverterSCSwitched CapacitorFETField Effect TransistorSBDSchottky Barrier DiodeSNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor        |

| BWBandwidthAMAmplitude ModulationDDirectivityFPAFocal Plane ArrayDUTDevice under TestBNBackground NoiseUCAUser Controlled AttenuationADCAnalog to Digital ConverterSCSwitched CapacitorFETField Effect TransistorSBDSchottky Barrier DiodeSNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor                                               |

| AMAmplitude ModulationDDirectivityFPAFocal Plane ArrayDUTDevice under TestBNBackground NoiseUCAUser Controlled AttenuationADCAnalog to Digital ConverterSCSwitched CapacitorFETField Effect TransistorSBDSchottky Barrier DiodeSNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor                                                          |

| DDirectivityFPAFocal Plane ArrayDUTDevice under TestBNBackground NoiseUCAUser Controlled AttenuationADCAnalog to Digital ConverterSCSwitched CapacitorFETField Effect TransistorSBDSchottky Barrier DiodeSNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor                                                                                |

| FPAFocal Plane ArrayDUTDevice under TestBNBackground NoiseUCAUser Controlled AttenuationADCAnalog to Digital ConverterSCSwitched CapacitorFETField Effect TransistorSBDSchottky Barrier DiodeSNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor                                                                                            |

| DUTDevice under TestBNBackground NoiseUCAUser Controlled AttenuationADCAnalog to Digital ConverterSCSwitched CapacitorFETField Effect TransistorSBDSchottky Barrier DiodeSNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor                                                                                                                |

| BNBackground NoiseUCAUser Controlled AttenuationADCAnalog to Digital ConverterSCSwitched CapacitorFETField Effect TransistorSBDSchottky Barrier DiodeSNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor                                                                                                                                    |

| UCAUser Controlled AttenuationADCAnalog to Digital ConverterSCSwitched CapacitorFETField Effect TransistorSBDSchottky Barrier DiodeSNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor                                                                                                                                                      |

| ADCAnalog to Digital ConverterSCSwitched CapacitorFETField Effect TransistorSBDSchottky Barrier DiodeSNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor                                                                                                                                                                                    |

| SCSwitched CapacitorFETField Effect TransistorSBDSchottky Barrier DiodeSNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor                                                                                                                                                                                                                  |

| FETField Effect TransistorSBDSchottky Barrier DiodeSNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor                                                                                                                                                                                                                                      |

| SBDSchottky Barrier DiodeSNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor                                                                                                                                                                                                                                                                |

| SNRSignal-to-Noise RatioHPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor                                                                                                                                                                                                                                                                                         |

| HPFHigh Pass FilterBPFBand Pass FilterLPFLow Pass FilterQFQuality Factor                                                                                                                                                                                                                                                                                                                 |

| BPFBand Pass FilterLPFLow Pass FilterQFQuality Factor                                                                                                                                                                                                                                                                                                                                    |

| LPFLow Pass FilterQFQuality Factor                                                                                                                                                                                                                                                                                                                                                       |

| QF Quality Factor                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                          |

| CT Continuous Time                                                                                                                                                                                                                                                                                                                                                                       |

| DT Discrete Time                                                                                                                                                                                                                                                                                                                                                                         |

| STF Signal Transfer Function                                                                                                                                                                                                                                                                                                                                                             |

| NTF Noise Transfer Function                                                                                                                                                                                                                                                                                                                                                              |

| PSD Power Spectral Density                                                                                                                                                                                                                                                                                                                                                               |

| OTA Operational Transconductance Amplifier                                                                                                                                                                                                                                                                                                                                               |

| CMFB   | Common Mode Feedback                                |

|--------|-----------------------------------------------------|

| СМ     | Common Mode                                         |

| PAC    | Periodic AC analysis                                |

| CW     | Continuous Wave                                     |

| GND    | Ground                                              |

| CMS    | Correlated Multiple Sampling                        |

| FD     | Fully Differential                                  |

| MC     | Monte Carlo                                         |

| FF     | Flip Flop                                           |

| SR     | Shift Register                                      |

| MUX    | Multiplexer                                         |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor   |

| MIM    | Metal Insulator Metal                               |

| RMS    | Root Mean Square                                    |

| AC     | Alternating current                                 |

| DC     | Direct current                                      |

| FoM    | Figure of Merits                                    |

| JSSC   | Journal of Solid-State Circuits                     |

| ISSCC  | International Solid State Circuits Conference       |

| IEEE   | Institute of Electrical and Electronics Engineers   |

| MOS    | Metal Oxide Semiconductor                           |

| NMOS   | N-channel MOSFET                                    |

| PMOS   | P-channel MOSFET                                    |

| SPCIE  | Simulation Program with Integrated Circuit Emphasis |

| MC     | Monte Carlo                                         |

| BSIM   | Berkeley Short-channel IGFET Mode                   |

| G      | Closed loop gain                                    |

| V <sub>IN</sub>             | Input Voltage                  |

|-----------------------------|--------------------------------|

| A                           | Amplitude                      |

| g <sub>m</sub>              | Small signal transconductance  |

| <b>g</b> <sub>DS</sub>      | Drain to source conductance    |

| r <sub>DS</sub>             | Drain to source resistance     |

| k                           | Boltzmann constant             |

| т                           | Temperature                    |

| К                           | Kelvin                         |

| С                           | Capacitance                    |

| I                           | Current                        |

| V                           | Voltage                        |

| V <sub>REF</sub>            | Reference Voltage              |

| V <sub>OUT</sub>            | Output Voltage                 |

| $\omega_0$                  | Angular frequency              |

| f <sub>center</sub>         | Center frequency               |

| S <sub>TH</sub> (f)         | Thermal noise spectral density |

| 1/f                         | Flicker noise                  |

| V <sub>OV</sub>             | Overdrive voltage              |

| V <sub>N</sub> <sup>2</sup> | Voltage noise power            |

| Ts                          | Sampling period                |

| η                           | Substrate factor               |

| λ                           | Wavelength                     |

| Q                           | Quality Factor                 |

| A <sub>0</sub>              | DC open loop gain              |

| f <sub>In</sub>             | Input frequency                |

| $\mathbf{f}_{clk}$          | clock frequency                |

| MATLAB                      | Matrix Laboratory              |

|                             |                                |

## **Table of Contents**

| Chapte | er 1: | Introduction1                                |

|--------|-------|----------------------------------------------|

| 1.1    | Elec  | ctromagnetic spectrum1                       |

| 1.2    | Pro   | perties of THz radiation2                    |

| 1.2    | .1    | Low Photon Energy2                           |

| 1.2    | .2    | High Penetration2                            |

| 1.2    | .3    | Atmospheric behavior2                        |

| 1.3    | THz   | Applications                                 |

| 1.3    | .1    | Imaging                                      |

| 1.3    | .2    | Quality control and non-destructive testing4 |

| 1.3    | .3    | Spectroscopy4                                |

| 1.3    | .4    | Communications5                              |

| 1.3    | .5    | Astronomy5                                   |

| 1.4    | THz   | Sources6                                     |

| 1.4    | .1    | Thermal Sources6                             |

| 1.4    | .2    | Electronic Sources                           |

| 1.4    | .3    | Optical Sources                              |

| 1.5    | THz   | Detectors9                                   |

| 1.5    | .1    | Heterodyne (Coherent) Detectors9             |

| 1.5    | .2    | Direct (Incoherent) Detectors 10             |

| 1.6    | Cha   | pter Summary                                 |

| Chapte | er 2: | Theory of CMOS based FET THz detection15     |

| 2.1    | Wh    | y CMOS?15                                    |

| 2.2    | Fiel  | d Effect Transistor as THz detector16        |

| 2.3    | Mat   | thematical Modeling of FET THz detector18    |

|     | 2.3        | .1    | Quasi Static Modeling                                              | 18 |

|-----|------------|-------|--------------------------------------------------------------------|----|

|     | 2.3        | .2    | Non-Quasi Static modeling                                          | 20 |

| 2   | .4         | Wh    | iy FET?                                                            | 22 |

| 2   | .5         | Cha   | apter Summary                                                      | 23 |

| Cha | apte       | er 3: | Measurement techniques for direct THz detectors                    | 24 |

| 3   | .1         | Rec   | quirements for Measurement Setup                                   | 24 |

| 3   | .2         | Ele   | ctrical and Optical performance parameters                         | 25 |

|     | 3.2        | .1    | Input power                                                        | 25 |

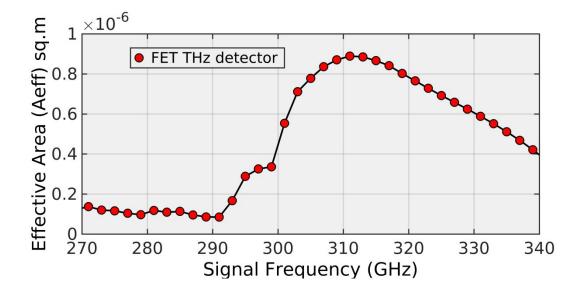

|     | 3.2        | .2    | Effective area                                                     | 26 |

|     | 3.2        | .3    | Polarization matching                                              | 26 |

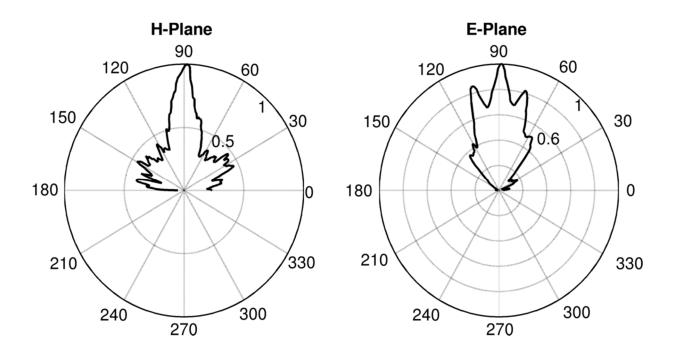

|     | 3.2        | .4    | Antenna directivity                                                | 27 |

| 3   | .3         | Me    | asurement of impinging power                                       | 27 |

|     | 3.3        | .1    | Method 1: Input power measurement using a reference detector       | 28 |

|     | 3.3<br>equ |       | Method 2: Input power density measurement using Friis transmission |    |

| 3   | .4         | Me    | asurement of effective area                                        | 32 |

|     | 3.4        | .1    | Method 1: Effective Area Measurement Using Antenna Directivity     | 33 |

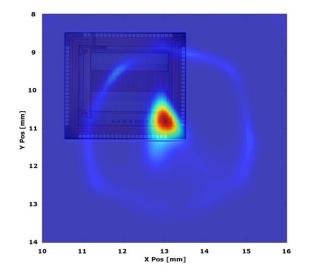

|     | 3.4        | .2    | Method 2: Effective Area Measurement Using Deconvolution           | 33 |

| 3   | .5         | Bac   | ckground Noise                                                     | 36 |

| 3   | .6         | Exa   | mple of fet characterization result                                | 38 |

|     | 3.6        | 5.1   | Voltage Responsivity and NEP                                       | 38 |

| 3   | .7         | Cha   | apter summary                                                      | 41 |

| Cha | apte       | er 4: | Simulation and Optimization of FET-based direct THz detectors      | 42 |

| 4   | .1         | Per   | formance Parameters of the Direct THz detectors                    | 42 |

|     | 4.1        | 1     | Responsivity (R)                                                   | 42 |

|     | 4.1        | 2     | Noise Equivalent Power (NEP)                                       | 43 |

|     | 4.1        | 3     | Dynamic Range                                                      | 43 |

| 4.2                                                         | SPI                                                                 | CE Simulations                                                                                                                                                                                                                                | 44                                                 |

|-------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 4.2                                                         | 2.1                                                                 | BSIM model                                                                                                                                                                                                                                    | 44                                                 |

| 4.2                                                         | 2.2                                                                 | EKV model                                                                                                                                                                                                                                     | 45                                                 |

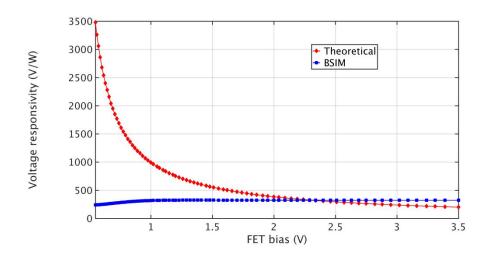

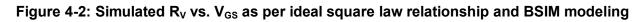

| 4.2                                                         | 2.3                                                                 | Voltage response                                                                                                                                                                                                                              | 47                                                 |

| 4.2                                                         | 2.4                                                                 | Current response                                                                                                                                                                                                                              | 47                                                 |

| 4.2                                                         | 2.5                                                                 | Simulated Noise Equivalent Power                                                                                                                                                                                                              | 49                                                 |

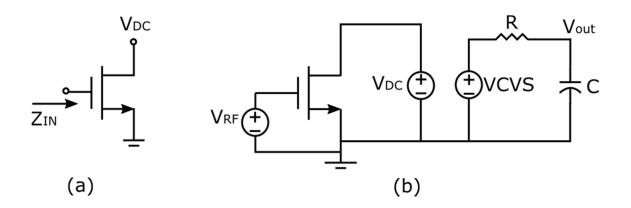

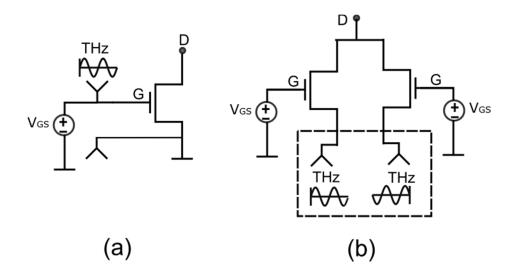

| 4.3                                                         | Sou                                                                 | urce driven and Gate driven configurations                                                                                                                                                                                                    | 50                                                 |

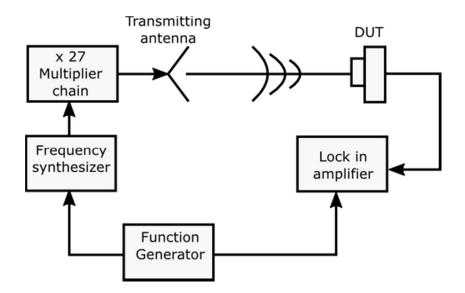

| 4.4                                                         | Me                                                                  | easurement Setup                                                                                                                                                                                                                              | 52                                                 |

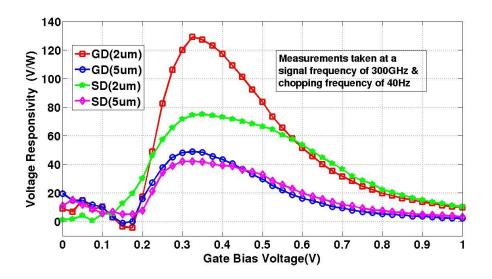

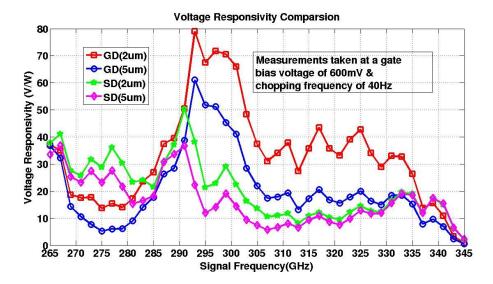

| 4.4                                                         | l.1                                                                 | Measurement Results                                                                                                                                                                                                                           | 52                                                 |

| 4.5                                                         | Dis                                                                 | cussion of the Results                                                                                                                                                                                                                        | 56                                                 |

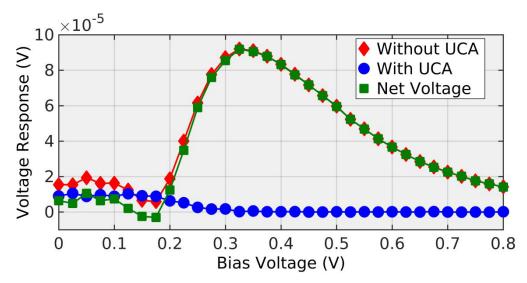

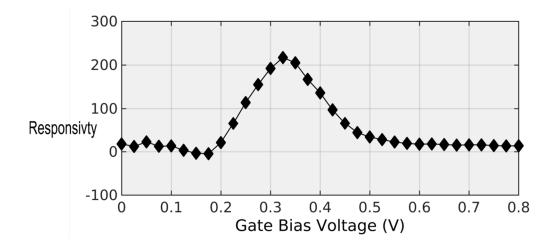

| 4.5                                                         | 5.1                                                                 | Biasing response                                                                                                                                                                                                                              | 56                                                 |

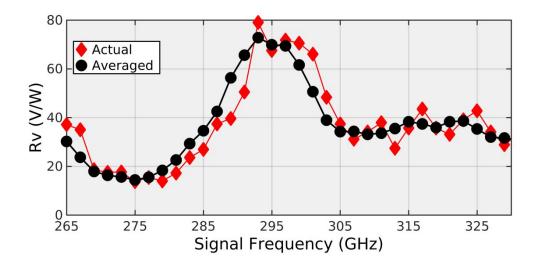

| 4.5                                                         | 5.2                                                                 | Frequency response                                                                                                                                                                                                                            | 56                                                 |

| 4.5                                                         | 5.3                                                                 | NEP                                                                                                                                                                                                                                           | 56                                                 |

| 4.6                                                         | Cha                                                                 | apter Summary                                                                                                                                                                                                                                 | 57                                                 |

|                                                             |                                                                     |                                                                                                                                                                                                                                               |                                                    |

| Chapte                                                      | er 5:                                                               | Single Pixel Design                                                                                                                                                                                                                           | 58                                                 |

| <b>Chapte</b><br>5.1                                        |                                                                     | Single Pixel Design                                                                                                                                                                                                                           |                                                    |

| •                                                           | Sta                                                                 |                                                                                                                                                                                                                                               | 59                                                 |

| 5.1                                                         | Sta<br>L.1                                                          | te-of-the-art review                                                                                                                                                                                                                          | 59<br>59                                           |

| 5.1<br>5.1                                                  | Sta<br>1.1<br>1.2                                                   | te-of-the-art review<br>Schuster, 2011, 3x4 imager                                                                                                                                                                                            | 59<br>59<br>60                                     |

| 5.1<br>5.1<br>5.1                                           | Sta<br>1.1<br>1.2<br>1.3                                            | ite-of-the-art review<br>Schuster, 2011, 3x4 imager<br>Ojefors, 2009, 3x5 Imager                                                                                                                                                              | 59<br>59<br>60<br>60                               |

| 5.1<br>5.1<br>5.1<br>5.1                                    | Sta<br>1.1<br>1.2<br>1.3<br>1.4                                     | te-of-the-art review<br>Schuster, 2011, 3x4 imager<br>Ojefors, 2009, 3x5 Imager<br>Hadi, 2012, A 1 k pixel camera                                                                                                                             | 59<br>59<br>60<br>60<br>61                         |

| 5.1<br>5.1<br>5.1<br>5.1<br>5.1                             | Sta<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5                              | te-of-the-art review<br>Schuster, 2011, 3x4 imager<br>Ojefors, 2009, 3x5 Imager<br>Hadi, 2012, A 1 k pixel camera<br>Boukhayma, 2014, 31 x 31 FPA                                                                                             | 59<br>59<br>60<br>60<br>61<br>62                   |

| 5.1<br>5.1<br>5.1<br>5.1<br>5.1<br>5.1                      | Sta<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>Pix                       | ate-of-the-art review<br>Schuster, 2011, 3x4 imager<br>Ojefors, 2009, 3x5 Imager<br>Hadi, 2012, A 1 k pixel camera<br>Boukhayma, 2014, 31 x 31 FPA<br>Kim, 2016, 8 x 8 Imager                                                                 | 59<br>59<br>60<br>61<br>62<br>62                   |

| 5.1<br>5.1<br>5.1<br>5.1<br>5.1<br>5.1<br>5.2               | Sta<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>Pix<br>2.1                | Ite-of-the-art review<br>Schuster, 2011, 3x4 imager<br>Ojefors, 2009, 3x5 Imager<br>Hadi, 2012, A 1 k pixel camera<br>Boukhayma, 2014, 31 x 31 FPA<br>Kim, 2016, 8 x 8 Imager<br>el specifications                                            | 59<br>59<br>60<br>61<br>62<br>62<br>64             |

| 5.1<br>5.1<br>5.1<br>5.1<br>5.1<br>5.1<br>5.2<br>5.2        | Sta<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>Pix<br>2.1<br>Cire        | Ite-of-the-art review<br>Schuster, 2011, 3x4 imager<br>Ojefors, 2009, 3x5 Imager<br>Hadi, 2012, A 1 k pixel camera<br>Boukhayma, 2014, 31 x 31 FPA<br>Kim, 2016, 8 x 8 Imager<br>el specifications<br>System level design                     | 59<br>59<br>60<br>61<br>62<br>62<br>64<br>66       |

| 5.1<br>5.1<br>5.1<br>5.1<br>5.1<br>5.1<br>5.2<br>5.2<br>5.3 | Sta<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>Pix<br>2.1<br>Cire<br>3.1 | te-of-the-art review<br>Schuster, 2011, 3x4 imager<br>Ojefors, 2009, 3x5 Imager<br>Hadi, 2012, A 1 k pixel camera<br>Boukhayma, 2014, 31 x 31 FPA<br>Kim, 2016, 8 x 8 Imager<br>el specifications<br>System level design<br>cuit level design | 59<br>59<br>60<br>61<br>62<br>62<br>64<br>66<br>66 |

|   | 5.4 | 4    | Chi  | p fabrication                           | . 75 |

|---|-----|------|------|-----------------------------------------|------|

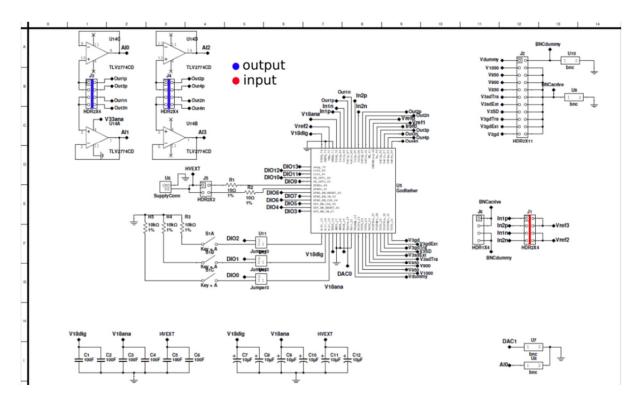

|   | [   | 5.4. | .1   | Electrical Interface                    | . 76 |

|   | [   | 5.4. | .2   | Test & measurement setup                | . 78 |

|   | 5.5 | 5    | Chi  | p characterization                      | . 78 |

|   | [   | 5.5. | .1   | Electrical Characterization             | . 79 |

|   | ļ   | 5.5. | .2   | THz characterization                    | . 80 |

|   | ļ   | 5.5. | .3   | Performance comparison with the SOA     | . 86 |

|   | 5.7 | 7    | Cha  | apter Summary                           | . 86 |

| С | haj | pte  | r 6: | THz imaging array                       | . 88 |

|   | 6.2 | 1    | Sys  | tem level design of the readout channel | . 88 |

|   | (   | 6.2. | .1   | Theoretical Analysis                    | . 89 |

|   | (   | 6.2. | .2   | Principle of operation                  | . 91 |

|   | 6.3 | 3    | Оре  | erational transconductance amplifier    | . 93 |

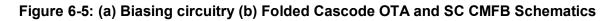

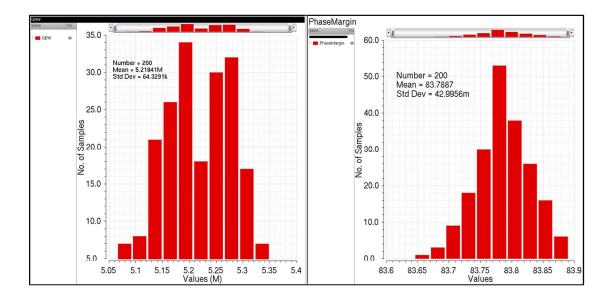

|   | (   | 6.3. | .1   | OTA simulation results                  | . 96 |

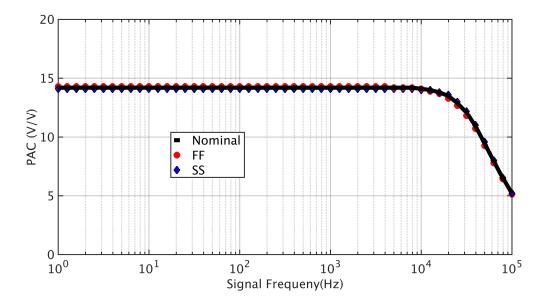

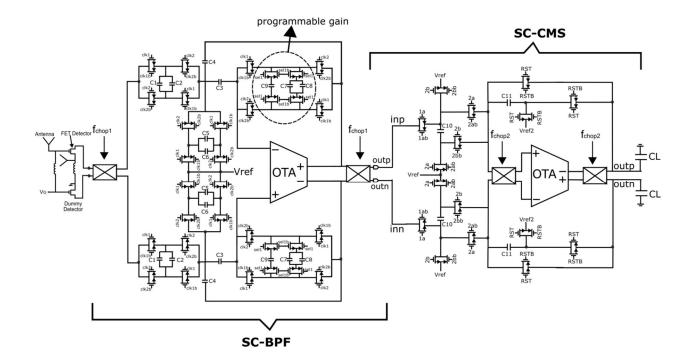

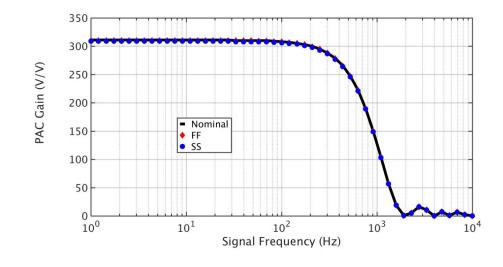

|   | (   | 6.3. | .2   | Simulation Results of the SC-BPF        | . 98 |

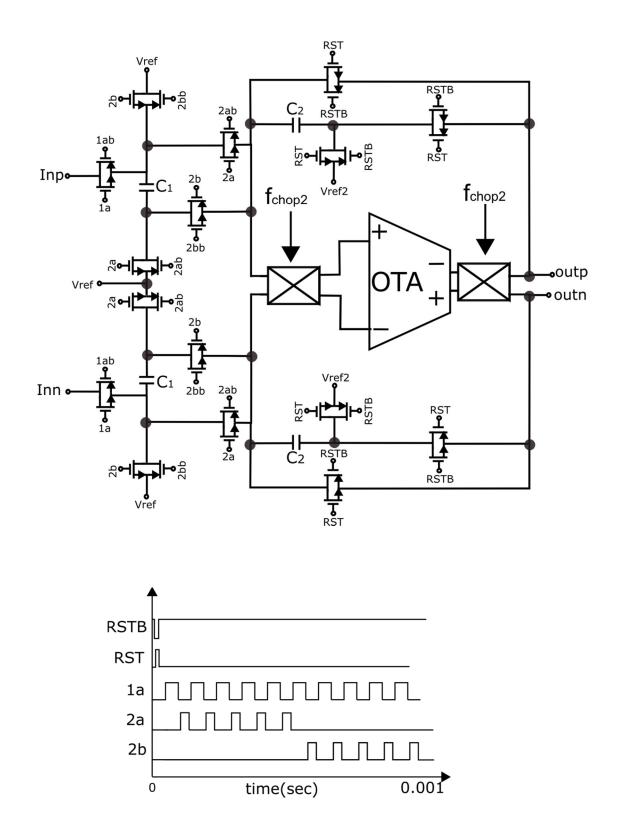

|   | 6.4 | 4    | Cor  | related multiple sampling               | . 99 |

|   | (   | 6.4. | .1   | Principle of operation                  | . 99 |

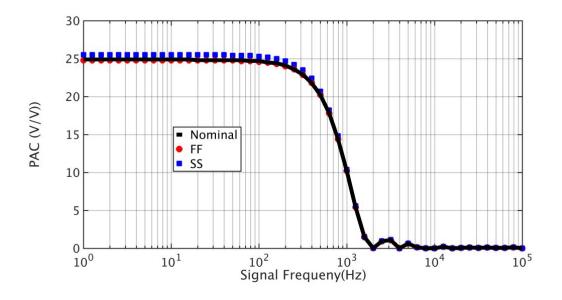

|   | (   | 6.4. | .2   | Simulation Results                      | 101  |

|   | 6.5 | 5    | Pixe | el schematic                            | 102  |

|   | (   | 6.5. | .1   | Simulation Results                      | 105  |

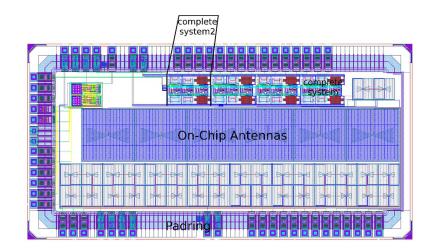

|   | 6.6 | 6    | THz  | z imaging array                         | 108  |

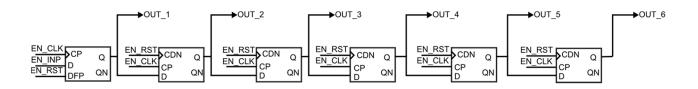

|   | (   | 6.6. | .1   | Shift Register                          | 108  |

|   | (   | 6.6. | .2   | Layout                                  | 109  |

|   | 6.7 | 7    | Chi  | p fabrication                           | 110  |

|   | (   | 6.7. | .1   | Electrical Interface                    | 111  |

|   | 6.8 | 8    | THz  | z characterization                      | 114  |

|   | 6.9 | 9    | Cha  | apter Summary                           | 118  |

| Chapte | er 7:  | Conclusion and Future Prospects                                     |     |

|--------|--------|---------------------------------------------------------------------|-----|

| Appen  | dix A: | OTA design using g <sub>m</sub> /i <sub>d</sub> methodology         |     |

| A.1    | Desig  | ning the amplifier using g <sub>m</sub> /i <sub>d</sub> methodology |     |

| A.2    | DC an  | alysis of the folded cascode OTA                                    | 125 |

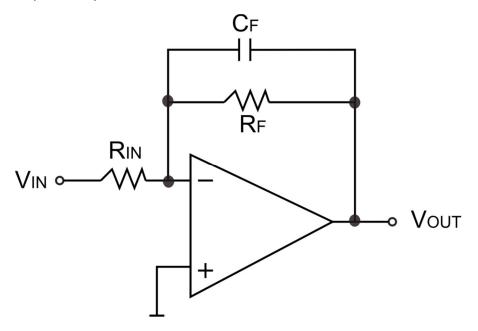

| Appen  | dix B: | Filter Design                                                       |     |

| B.1    | High F | Pass Filter                                                         |     |

| B.2    | Low P  | ass Filter (LPF) Design                                             |     |

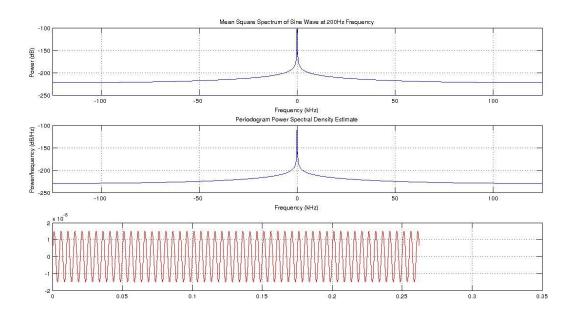

| Appen  | dix C: | System level simulations                                            |     |

| C.1    | MATL   | AB Code                                                             |     |

| C.2    | SIMU   | LATION                                                              |     |

| Refe   | rences |                                                                     |     |

# **List of Figures**

| Figure 1-1: Electromagnetic Spectrum [3]1                                                                   |

|-------------------------------------------------------------------------------------------------------------|

| Figure 1-2: Graph showing the atmospheric attenuation as a function of frequency at sea level [7]           |

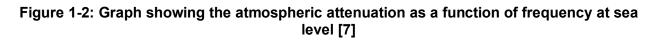

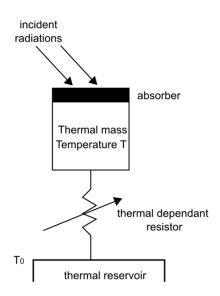

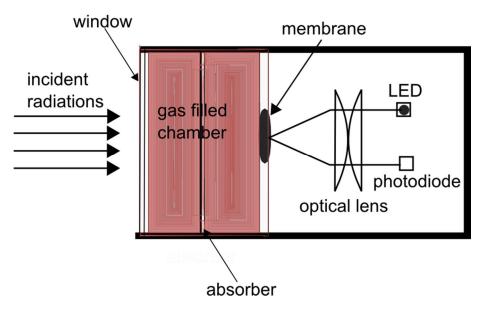

| Figure 1-3: Schematic showing the operation of bolometer11                                                  |

| Figure 1-4: Schematic showing the operation of golay cell                                                   |

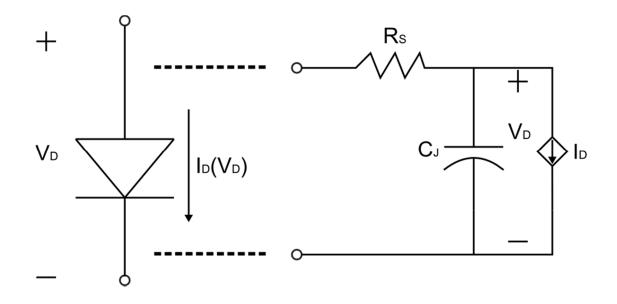

| Figure 1-5: Schottky Barrier Diode and its small signal model                                               |

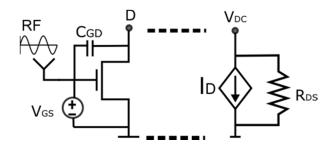

| Figure 2-1: Quasi Static modeling of the FET device in RF range                                             |

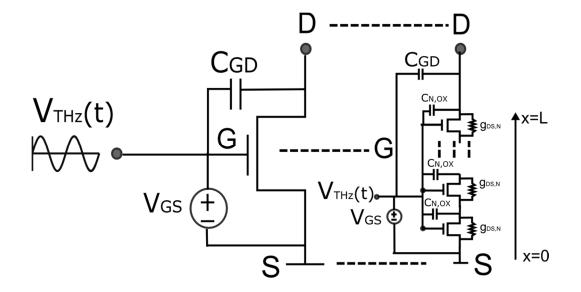

| Figure 2-2: Non Quasi Static model of the FET device in the THz frequency range21                           |

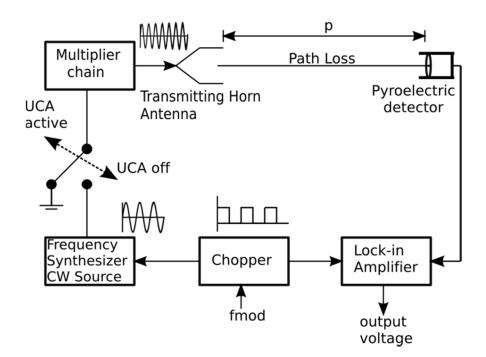

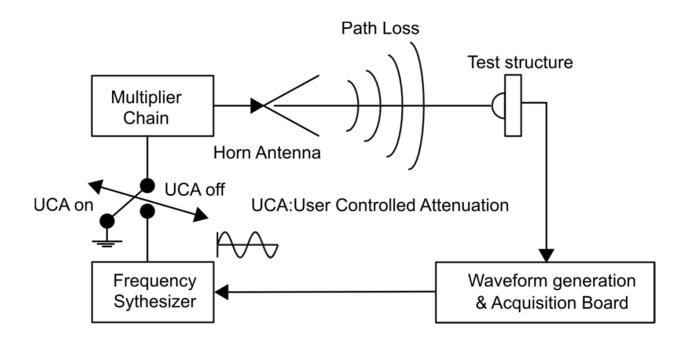

| Figure 3-1: Test and measurement setup used to characterize direct THz detectors 28                         |

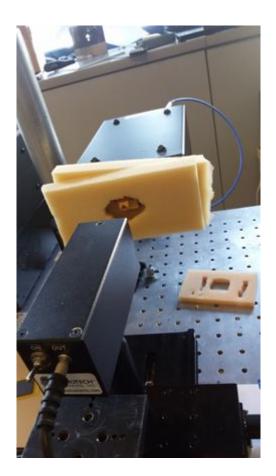

| Figure 3-2 Laboratory setup involving a THz source and pyroelectric detector 29                             |

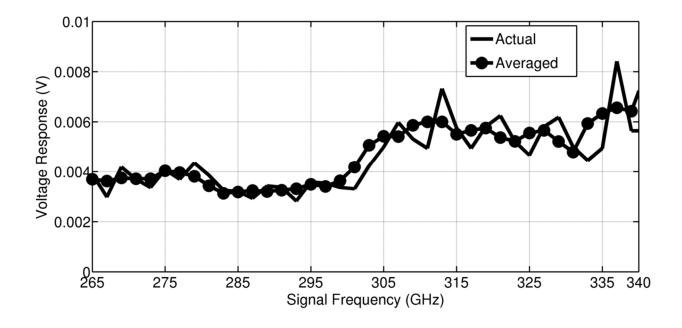

| Figure 3-3: Measured voltage response of the reference (pyroelectric) detector vs. THz signal               |

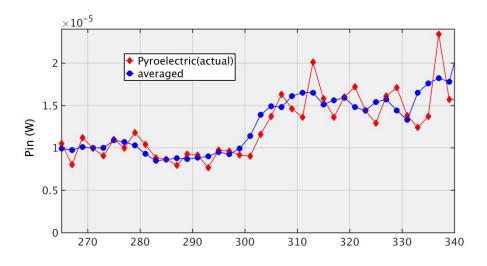

| Figure 3-4: Input power of pyroelectric detector vs. signal frequency                                       |

|                                                                                                             |

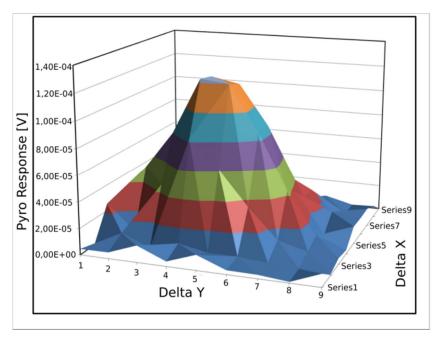

| Figure 3-5: Spatial Distribution plot of the pyroelectric response for the sourcecharacterization method.31 |

|                                                                                                             |

| characterization method                                                                                     |

| Figure 4-1: Simulation setup used to determine the performance parameters 44                                               |

|----------------------------------------------------------------------------------------------------------------------------|

| Figure 4-2: Simulated $R_V$ vs. $V_{GS}$ as per ideal square law relationship and BSIM modeling                            |

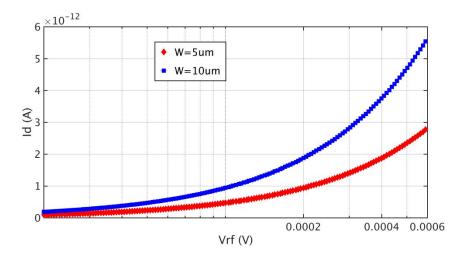

| Figure 4-3: Id vs. Vrf when FET is simulated with 600 GHz frequency signal at 1V bias voltage                              |

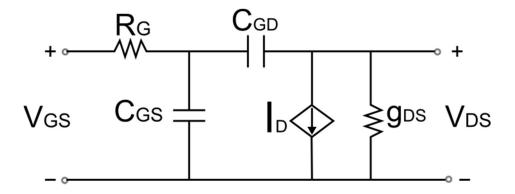

| Figure 4-4: FET small signal model                                                                                         |

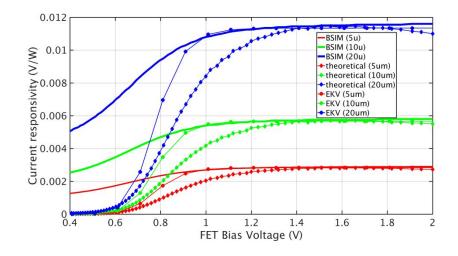

| Figure 4-5: Simulated R <sub>I</sub> vs. V <sub>GS</sub> for varying device widths                                         |

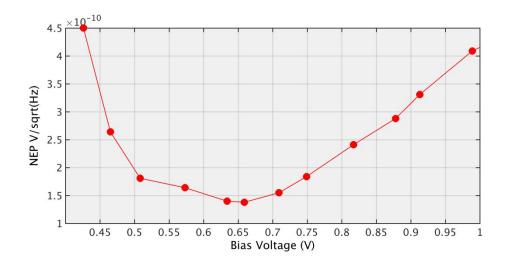

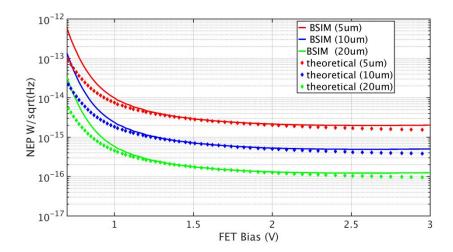

| Figure 4-6: Simulated NEP (W/VHz) vs. V <sub>GS</sub> 50                                                                   |

| Figure 4-7: FET based (a) gate driven and (b) source driven configurations                                                 |

| Figure 4-8: Setup for THz measurements52                                                                                   |

| Figure 4-9: Voltage responsivity graphs of GD and SD structures with different dimensions vs. Gate bias                    |

| Figure 4-10: Voltage responsivity graphs of GD and SD structures with different dimensions vs. Signal frequency            |

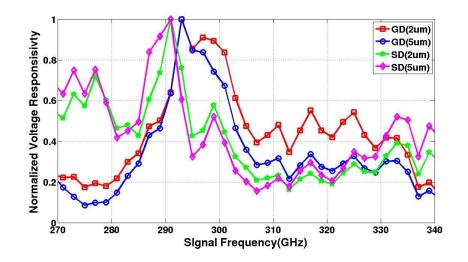

| Figure 4-11: Normalized responsivity graphs of GD and SD structures with different dimensions vs. Signal frequency         |

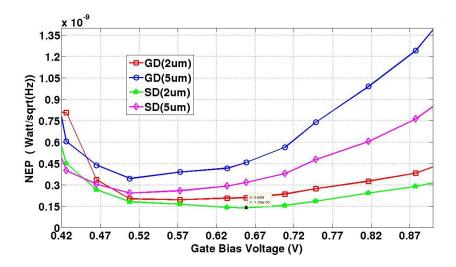

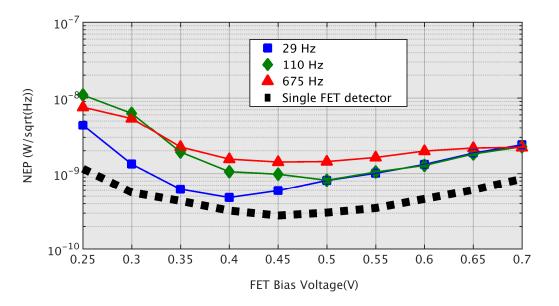

| Figure 4-12: NEP of test structures as a function of FET gate bias voltage                                                 |

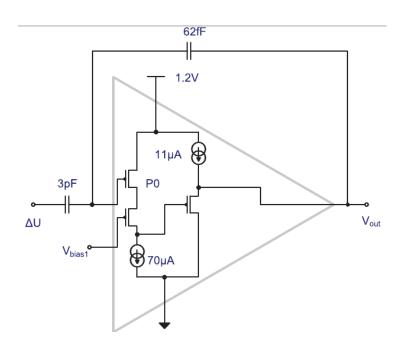

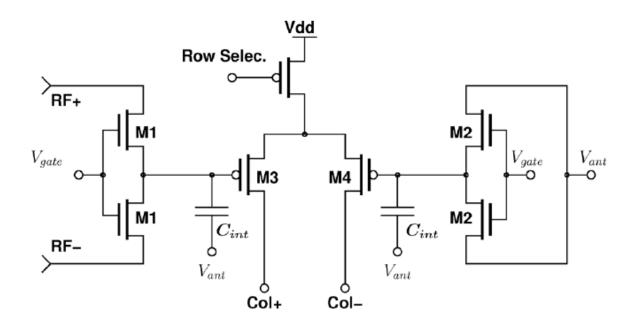

| Figure 5-1: In pixel amplifier schematic used in [67]59                                                                    |

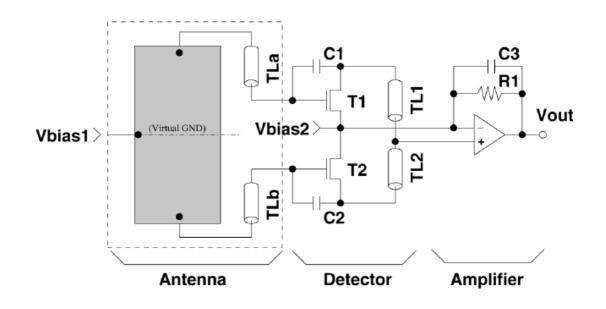

| Figure 5-2: Pixel schematic comprising an on-chip differential antenna, FET detectors and voltage amplifier used in [65]60 |

| Figure 5-3: Pixel schematic of the differential cascode configuration used in [93] 61                                      |

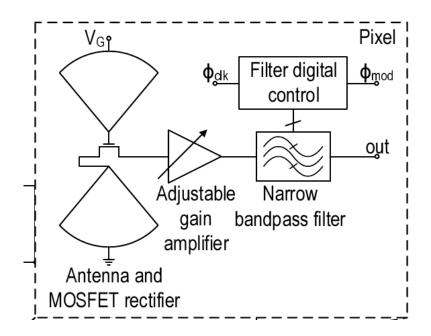

| Figure 5-4: System level design of the pixel used in [94] [95]62                                                           |

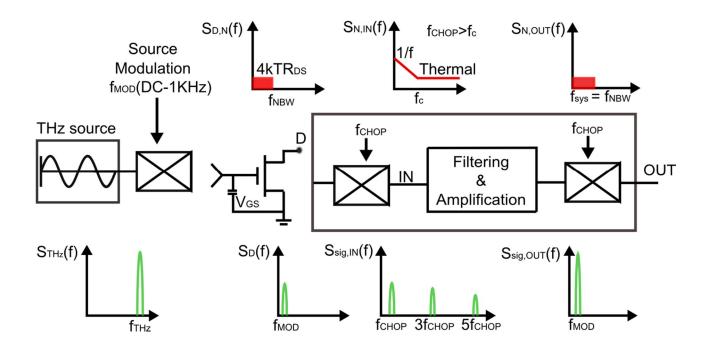

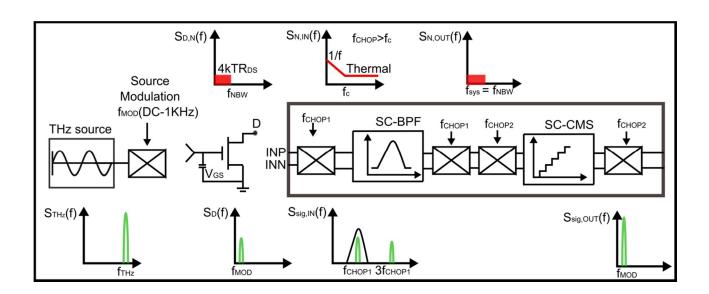

| Figure 5-5: System level design of the pixel showing the signal and noise spectra alongside different stages               |

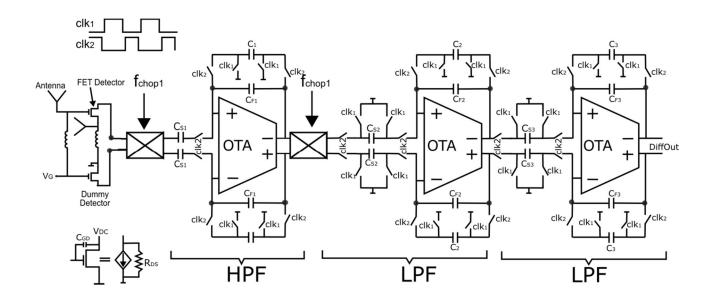

| Figure 5-6: Circuit schematic of the pixel showing antenna-coupled FET detectors and SC based multistage readout interface |

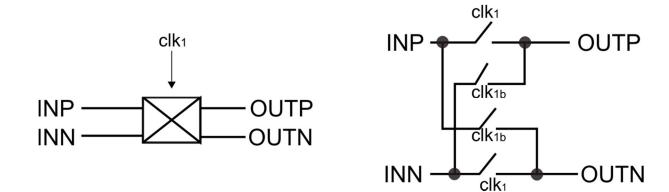

| Figure 5-7: Chopper symbol and circuit schematic                                                                           |

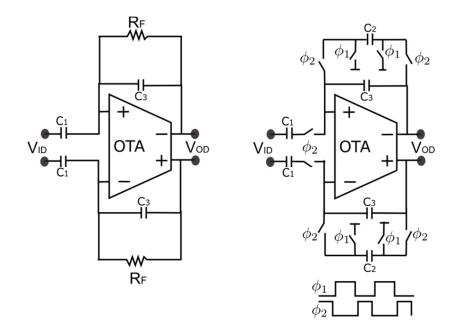

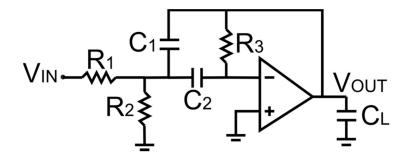

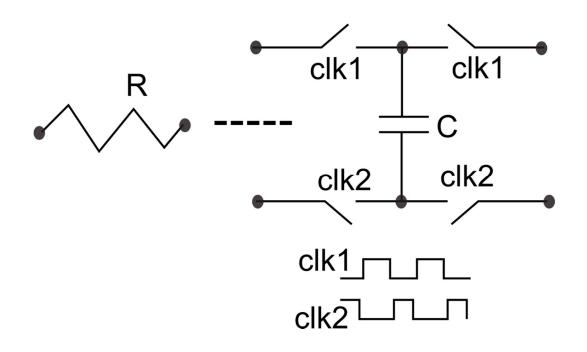

| Figure 5-8: Circuit schematic of the switched capacitor high passes filter and non-<br>overlapping clock signals           |

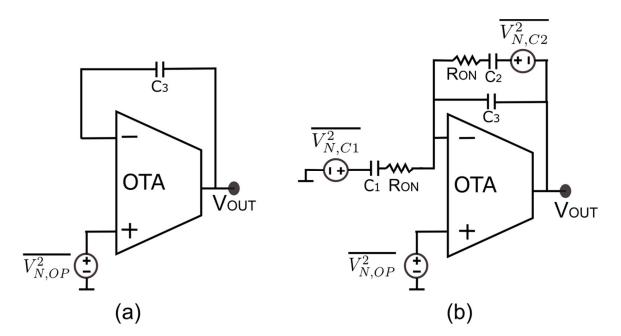

| Figure 5-9: Configurations of the first stage SC-HPF for noise analysis                                                  |

|--------------------------------------------------------------------------------------------------------------------------|

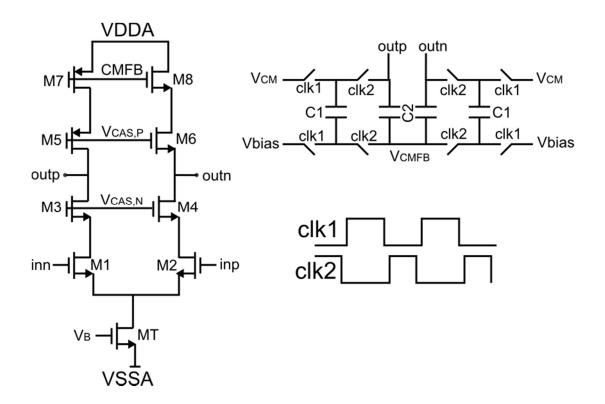

| Figure 5-10: Telescopic cascode OTA and SC-CMFB with non-overlapping clocks 73                                           |

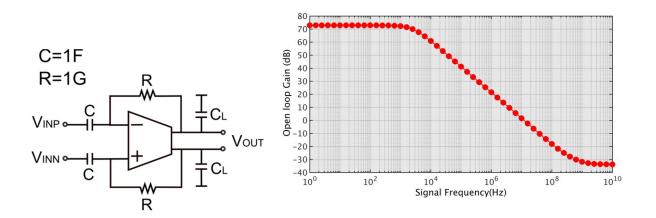

| Figure 5-11: Simulated frequency response of OTA in open loop configuration and the testbench74                          |

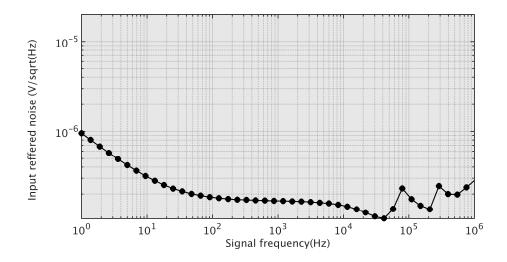

| Figure 5-12: Simulated frequency response of OTA in open loop configuration74                                            |

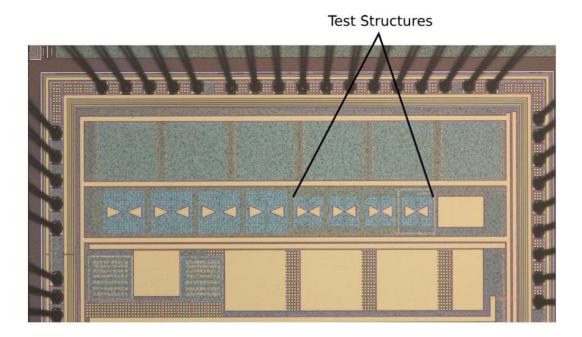

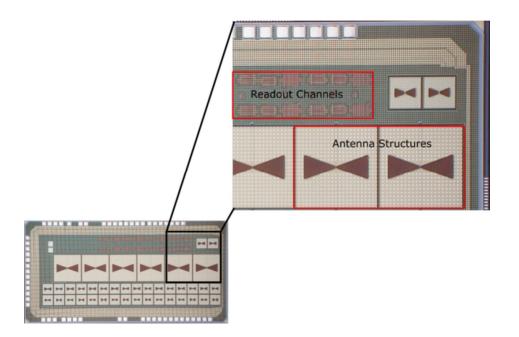

| Figure 5-13: Chip micrograph (Inset shows the fabricated antennae and the readout channels)75                            |

| Figure 5-14: Chip layout showing the antenna, readout and the padring                                                    |

| Figure 5-15: Daughter board for chip characterization78                                                                  |

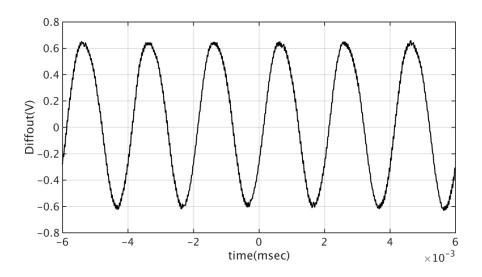

| Figure 5-16: Differential transient output of the pixel when stimulated by 400 $\mu V_{\mbox{\scriptsize PP}}$ sine wave |

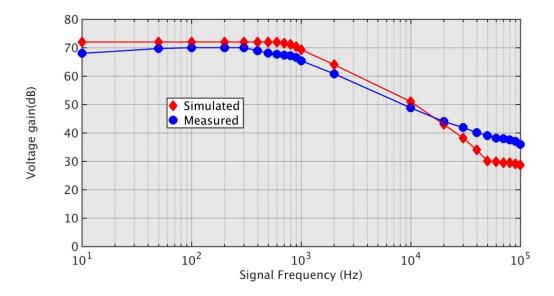

| Figure 5-17: PAC simulated and measured frequency response of the pixel                                                  |

| Figure 5-18: Test and measurement setup for THz pixel                                                                    |

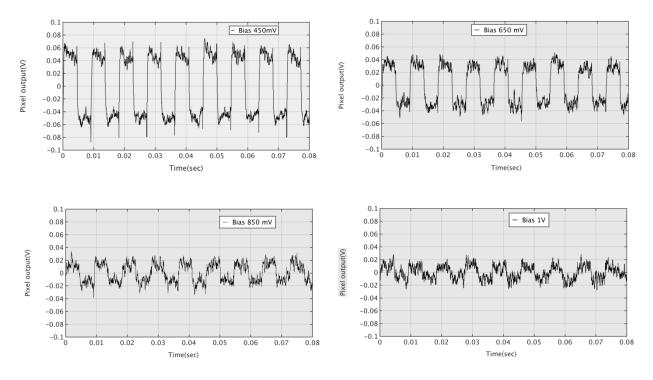

| Figure 5-19: Pixel output at different gate bias voltages when illuminated with THz radiation                            |

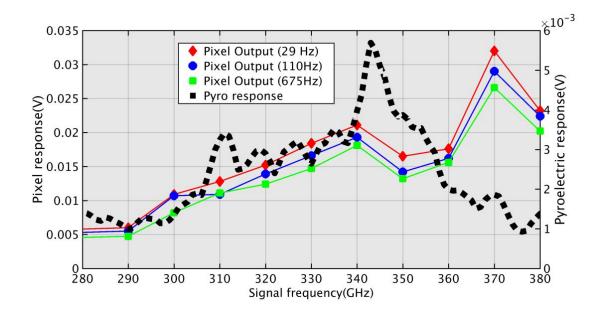

| Figure 5-20: Pixel response as a function of THz frequency. The pyroelectric response (averaged) is also shown           |

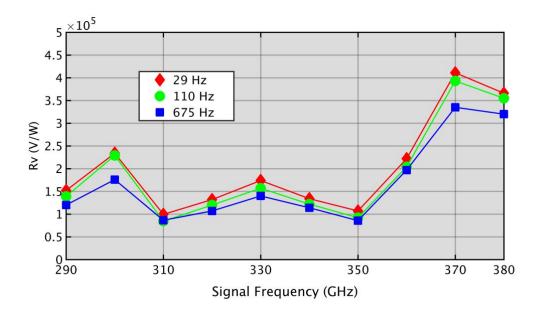

| Figure 5-21: Voltage responsivity as a function of THz source frequency                                                  |

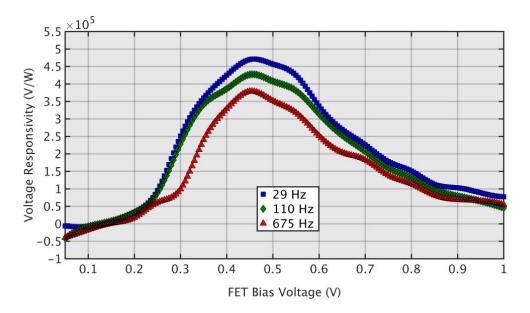

| Figure 5-22: Voltage responsivity as a function of FET gate bias                                                         |

| Figure 5-23: NEP as a function of FET gate bias85                                                                        |

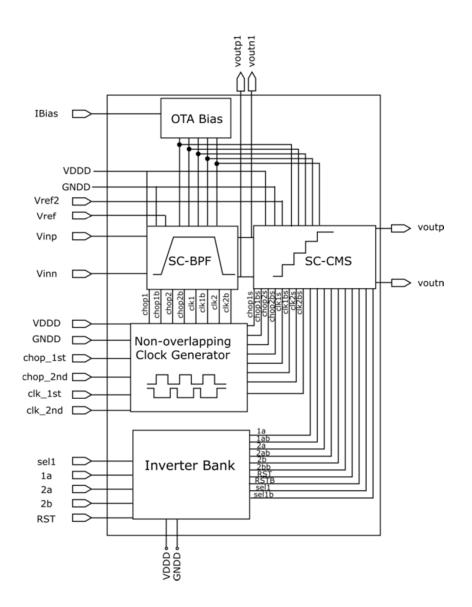

| Figure 6-1: System level design of the readout channel                                                                   |

| Figure 6-2: Single ended CT-BPF prototype90                                                                              |

| Figure 6-3: SC Equivalence of a resistor91                                                                               |

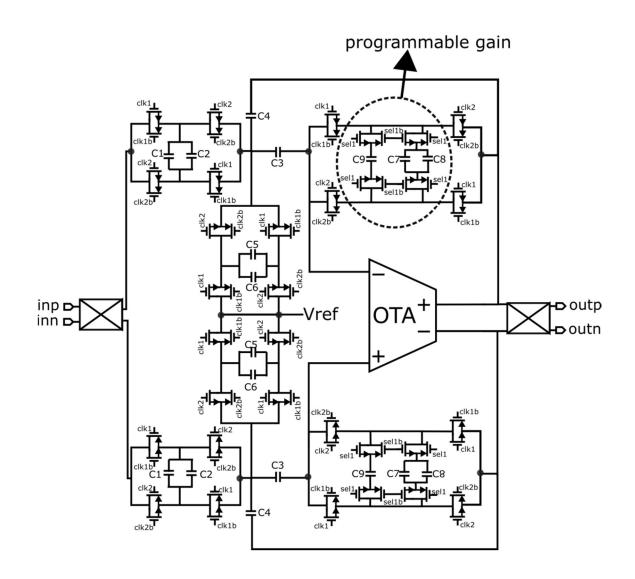

| Figure 6-4: Chopper-stabilized FD SC-BPF based on the CT prototype of Figure-6.2.92                                      |

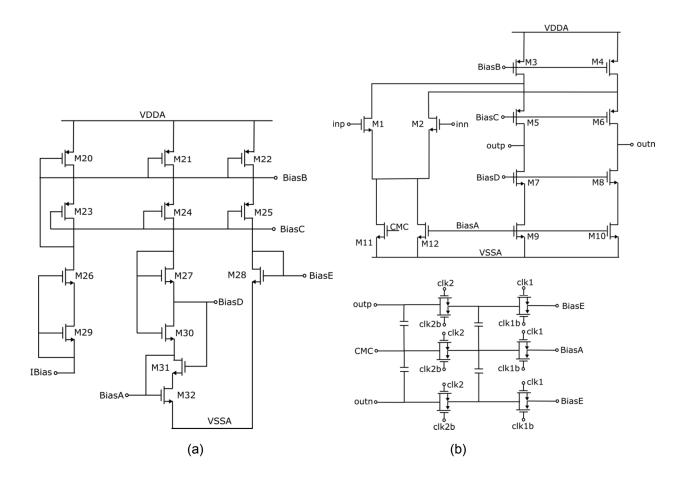

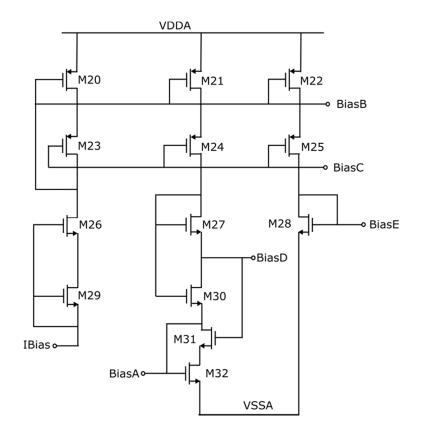

| Figure 6-5: (a) Biasing circuitry (b) Folded Cascode OTA and SC CMFB Schematics 93                                       |

| Figure 6-6: Open loop frequency response of the OTA96                                                                    |

| Figure 6-7: MonteCarlo simulations of the folded cascode OTA GBW and PM98                                                |

| Figure 6-8: PAC gain of SC-BPF                                                                                           |

| Figure 6-9: Circuit diagram of the SC-CMS (top) and the transient signal (bottom) 100                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6-10: PAC simulated frequency response of SC-CMS                                                                                                                                               |

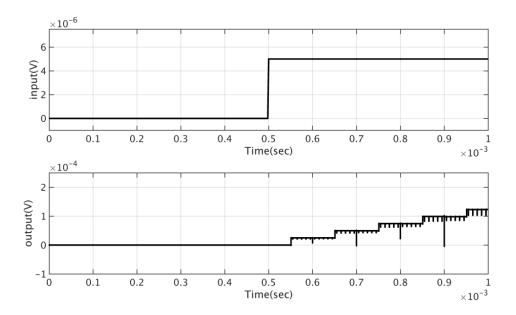

| Figure 6-11: Simulated time response of SC-CMS when stimulated with 5µVPP input signal                                                                                                                |

| Figure 6-12: Circuit diagram of pixel schematic                                                                                                                                                       |

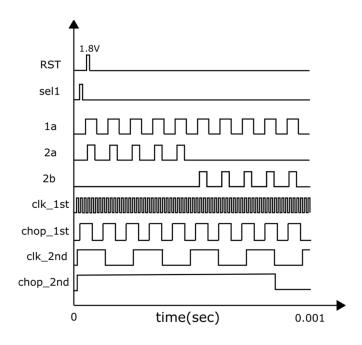

| Figure 6-13: Timing waveforms 104                                                                                                                                                                     |

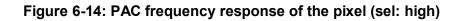

| Figure 6-14: PAC frequency response of the pixel (sel: high)105                                                                                                                                       |

| Figure 6-15: Transient response of the pixel when stimulated with 5µV input signal (sel: low)                                                                                                         |

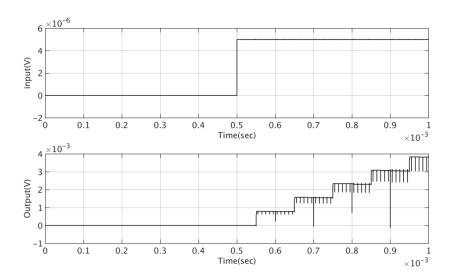

| Figure 6-16: MC simulations of the pixel showing the presence of an input offset saturating the readout channel in the presence of (a) no input signal (b) $2.5\mu$ V and (c) $100\mu$ V input signal |

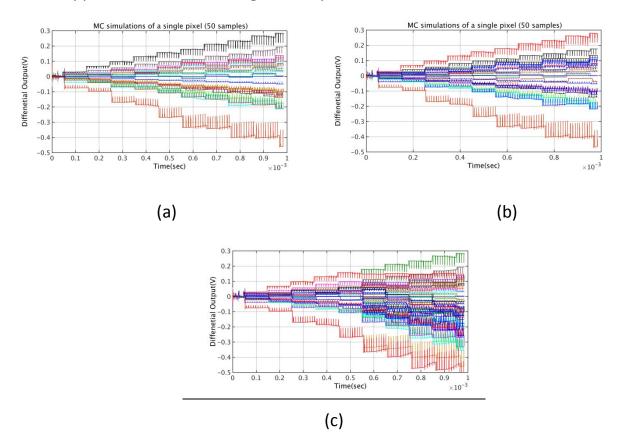

| Figure 6-17: MC simulations of the pixel with a chopper stabilized SC-CMS stage in the presence of (a) no input signal (b) $2.5\mu$ V al and (c) $100\mu$ V input signal 107                          |

| Figure 6-18: An 8 x 6 THz imaging array and the relevant building blocks                                                                                                                              |

| Figure 6-19: A 6-bit SR configuration109                                                                                                                                                              |

| Figure 6-20: Layout of the single pixel including the on-chip antenna                                                                                                                                 |

| Figure 6-21: Chip: Core and Padring 110                                                                                                                                                               |

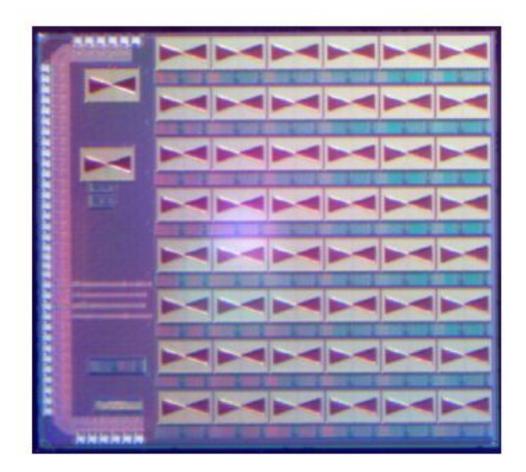

| Figure 6-22: Chip micrograph: showing the readout channel test structure and imaging array                                                                                                            |

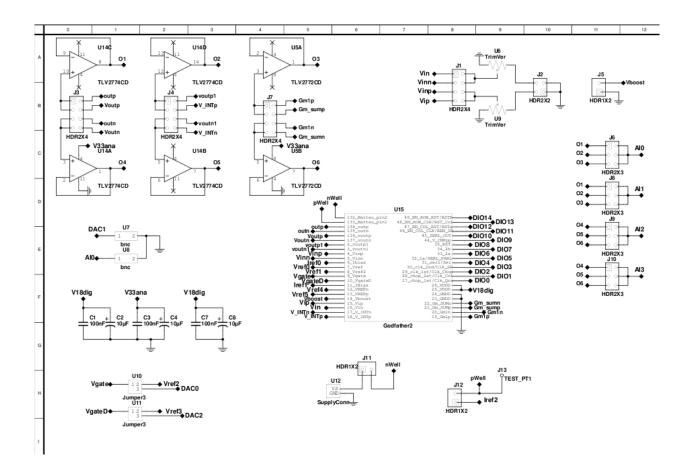

| Figure 6-23: Test bench for the measurement and debugging of single pixel and 8 x 6 THz array                                                                                                         |

| Figure 6-24: Designed daughter board 114                                                                                                                                                              |

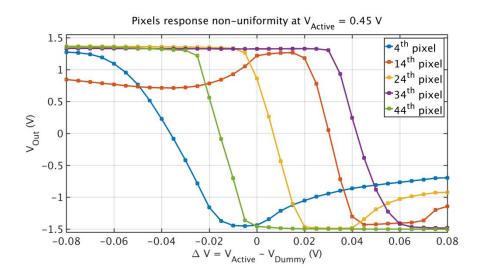

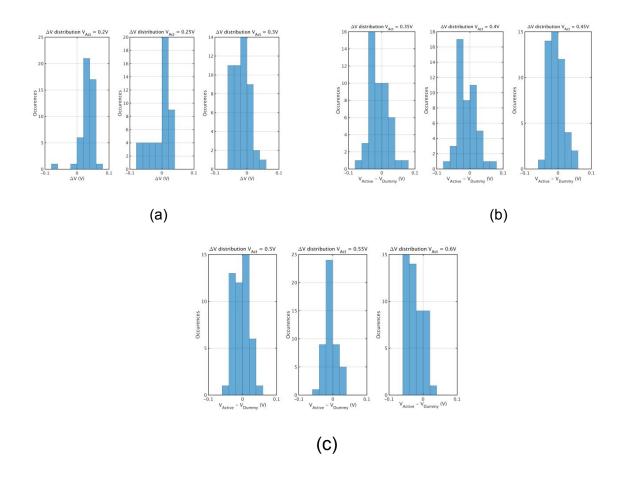

| Figure 6-25: Non-uniformity of different pixel response vs. gate bias difference 115                                                                                                                  |

| Figure 6-26: Distribution plots of various pixels as a function of bias voltage 116                                                                                                                   |

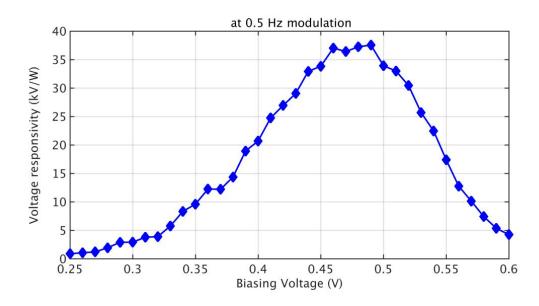

| Figure 6-27: Voltage responsivity vs. FET gate bias at 325 GHz signal frequency 117                                                                                                                   |

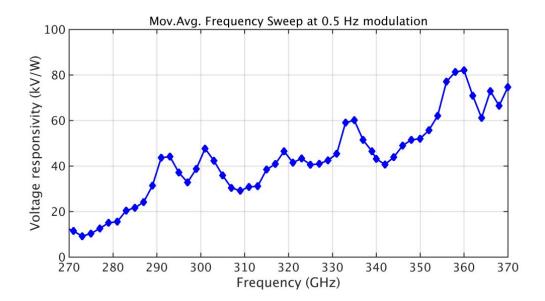

| Figure 6-28: Pixel voltage responsivity vs. THz signal frequency at 0.45V bias 117                                                                                                                    |

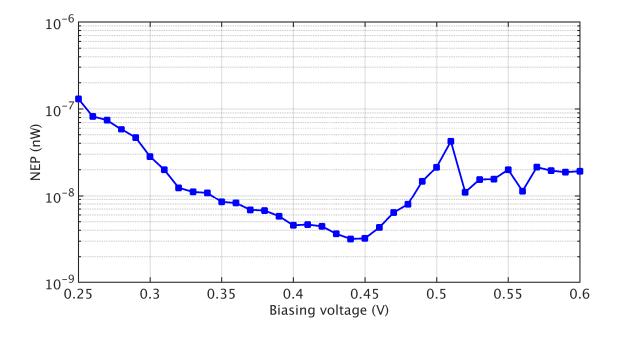

| Figure 6-29: Pixel NEP vs. FET gate bias at 325 GHz signal frequency                                                                                                                                  |

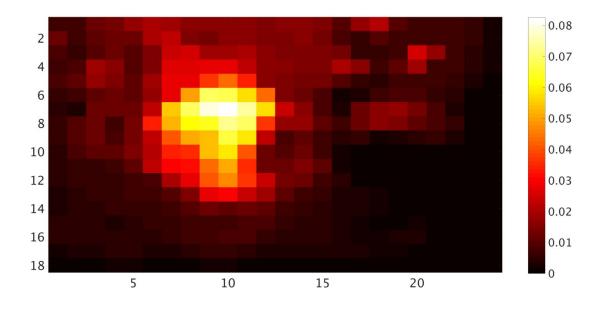

| Figure 6-30: Stitching of 3x3 images of the THz spot produced by the source 119                                                                                                                       |

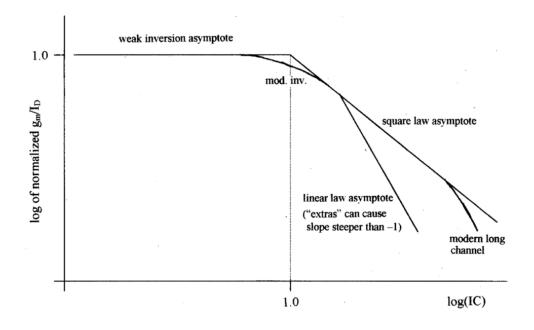

| Figure A-1: Transconductance efficiency vs. Inversion coefficient [103]                                 |

|---------------------------------------------------------------------------------------------------------|

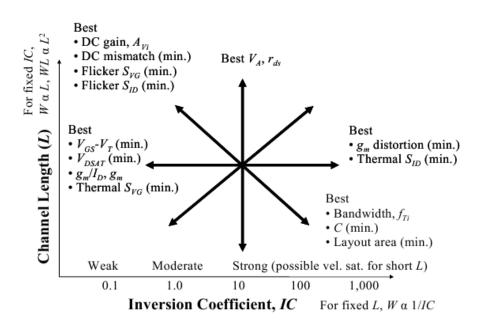

| Figure A-2: Operating space of the device with respect to channel length and IC [102]                   |

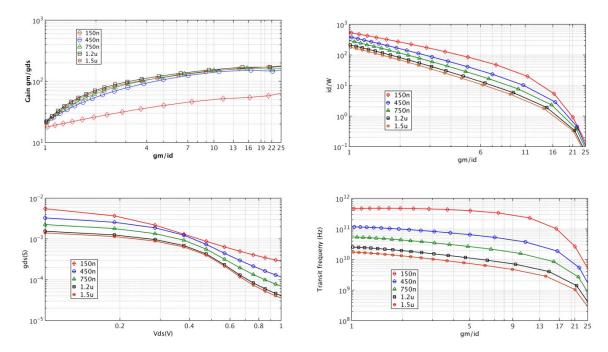

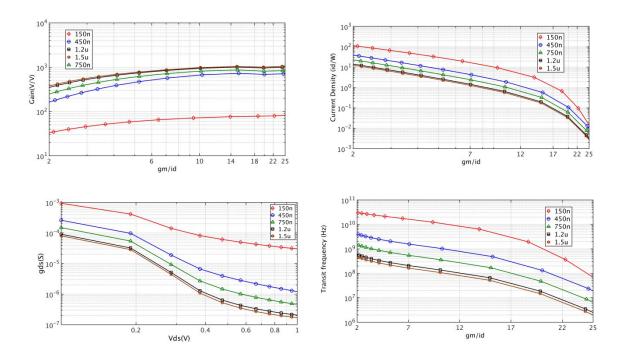

| Figure A-3: Simulated parameters of NMOS transistors for $g_m/i_d$ design at different channel length L |

| Figure A-4: Simulated parameters of PMOS transistors for $g_m/i_d$ design at different channel length L |

| Figure A-5: OTA biasing circuitry126                                                                    |

| Figure B-1: CT-LPF prototype128                                                                         |

| Figure C-1: Simulated plot of input sinusoidal waveform                                                 |

| Figure C-2: Simulated plot of square waveform139                                                        |

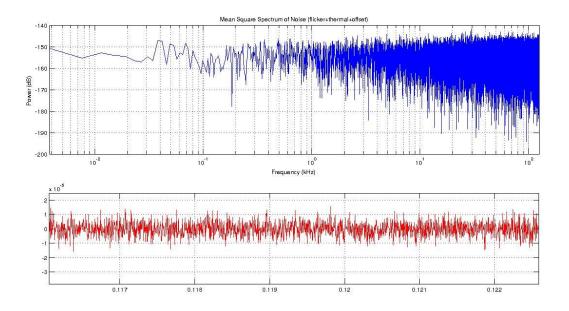

| Figure C-3: PSD plot of the generated noise (thermal, flicker and offset)                               |

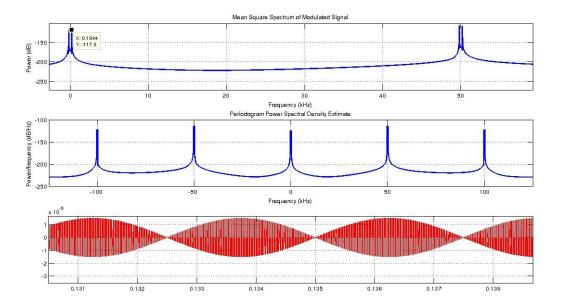

| Figure C-4: simulated plot of the modulated signal140                                                   |

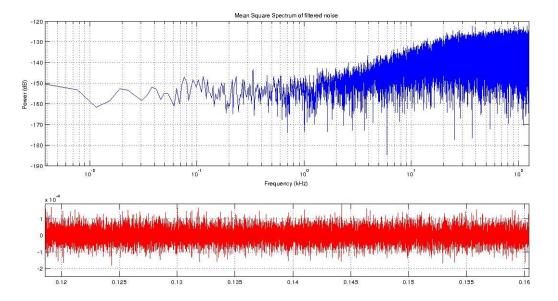

| Figure C-5: simulated plot of the filtered noise140                                                     |

| Figure C-6: simulated plot of the filtered signal and noise                                             |

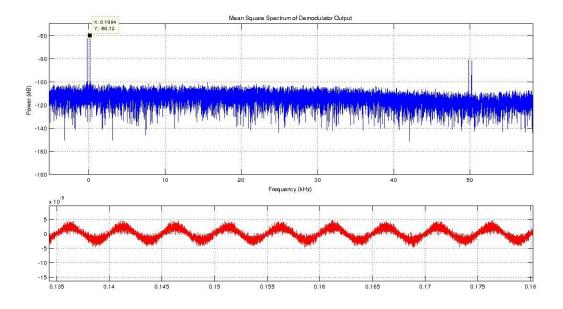

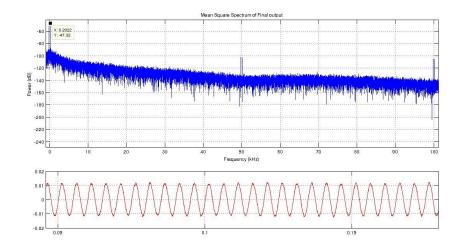

| Figure C-7: Final output141                                                                             |

### **List of Tables**

| Table 1-1: Characteristics of various THz sources       9                                                    |

|--------------------------------------------------------------------------------------------------------------|

| Table 1-2: Characteristics of various THz detectors       14                                                 |

| Table 4-1: Technology and device parameters       45                                                         |

| Table 4-2: Measured performance parameters of the FET structures in differentconfigurations and dimensions55 |

| Table 5-1: System level specifications of the readout interface         64                                   |

| Table 5-2: System & circuit level design specifications of individual stages                                 |

| Table 5-3: OTA design specifications72                                                                       |

| Table 5-4: Theoretical and simulation design details of the telescopic cascode OTA 72                        |

| Table 5-5: Pins description77                                                                                |

| Table 5-6: Comparison with the state-of-art                                                                  |

| Table 6-1: OTA system level specifications         94                                                        |

| Table 6-2: OTA: device level specifications       94                                                         |

| Table 6-3: OTA bias: device level specifications                                                             |

| Table 6-4: Noise contribution of OTA devices       97                                                        |

| Table 6-5: System level specifications       103                                                             |

| Table 6-6: Capacitor values    103                                                                           |

| Table 6-7: Pins name and description112                                                                      |

xxvii

### **CHAPTER 1: INTRODUCTION**

#### 1.1 ELECTROMAGNETIC SPECTRUM

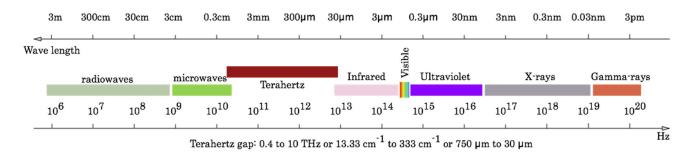

THz attracted vast scientific research and experimental interests primarily due to its nature of behavior that, at times, is at odds with the rest of the electromagnetic spectrum. Figure 1-1 shows the Electromagnetic (EM) Spectrum on the frequency and wavelength axes depicting the frequency range of different regions. The Terahertz range (THz) correspond to the waves oscillating at the rate of  $10^{12}$  oscillations or periods per second and it lies between the millimeter-wave and far-infrared (IR) regions on its lower and upper end of the spectrum, respectively. The boundaries of this region are generally defined between 300 GHz (1000µm) to 10 THz (30 µm) [1] [2]. Thanks to its several intrinsic behavioral properties, the THz region had specially been of keen interest to the physicists and scientists for long time dating as far back as the early 19<sup>th</sup> century.

Figure 1-1: Electromagnetic Spectrum [3]

From historical perspective, the realization of the THz systems and their prototypes has proven to be quite difficult. Indeed, in and below its neighboring millimeterwave region, many electronic and RF systems for signal generation, detection, and amplification are reported. Thanks to the scalability and low cost of these technologies, these systems make up the very basis of many commercial applications for large scale manufacturing, especially in communication systems. On the other hand, well-known optical techniques are employed to cover the far-IR region. However, unlike these two, the THz region had been marked with the lack of solid-state devices that could be used for efficient signal generation and THz detection at room temperature, and hence the name 'THz gap' was originated. Despite of this difficulty, there has been an interest to explore and bridge this gap, mainly because of many peculiar properties which are explained in details in the following paragraphs [4] [5].

#### **1.2 PROPERTIES OF THZ RADIATION**

#### 1.2.1 Low Photon Energy

THz waves carry very low photon energy. At 1 THz, the energy carried by the photons is only 4 milli-electron volt (meV): this level is extremely low, for example compared to the X-rays that carry up to several keV of energy. Such low levels of energy cannot cause ionization which makes the use of THz technology harmless to human body tissues. However, low energy levels also make it very difficult to detect THz radiation.

#### 1.2.2 High Penetration

THz radiation can penetrate through many non-metallic and nonpolar materials including plastic, clothing and wood but they are reflected back from the metals. This property enables THz systems to see through packaging to find out hidden and concealed object [6]. Many materials, such as explosives, dangerous chemical substances and biological agents have characteristics THz spectra which can be used to detect the fingerprint, thus allowing the detection of these substances.

#### 1.2.3 Atmospheric behavior

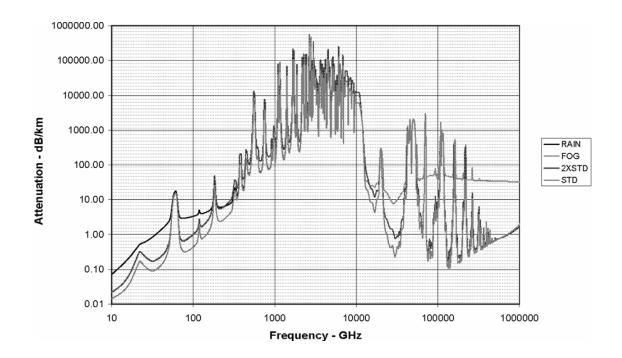

THz radiations have high water absorption coefficient and they are scattered from water molecules which means that they can be severely attenuated while propagating through the atmosphere [7].

Figure 1-2 shows the behavior of the THz radiations on their interaction with water molecules which shows that the attenuation is dependent on the concentration of water vapors and the THz region (especially from 1 - 10 THz) suffers from the highest atmospheric attenuation. It is also worth noticing that attenuation is dependent on water vapors and the effects of fog and rain cannot be easily

distinguished. Indeed, atmospheric attenuation effects both passive and active imaging applications with the possible reduction in the SNR value in the sensor image.

#### **1.3 THZ APPLICATIONS**

#### 1.3.1 Imaging

Low photon energy and ability to penetrate specific materials make the THz region useful for imaging applications, especially in the defense and security fields [8] [9]. THz imaging systems can be employed as body scanners at airports, sensitive installations and important buildings [10] [11], making them a complementary solution in addition to X-ray screening and other types of metal detectors. However, low photon energy also reduces the quantum efficiency of the THz detectors which makes it very challenging to design suitable readout architectures for imaging systems [12].

Medical and biomedical imaging is another field that can be potentially benefitted from THz imaging systems. Again, thanks to their low energy and high spectral resolution, THz radiation is safe to use for human body tissues but the water contents in these tissues hamper imaging. THz radiations can also be employed to analyze and reveal various chemical and biological phenomena [13]. For example, due to the large absorption coefficient of water, measurement of water contents in a plant is one potential application. Another application involves analyzing various kinds of cancers, including liver and breast cancer cells [14].

#### 1.3.2 Quality control and non-destructive testing

Every material is made up of atoms and molecules that are combined together by chemical bonding. These bonds can vibrate at their characteristics frequency when exposed to electromagnetic radiation of certain wavelength. Indeed, information about their properties and composition, as well as impurities of the substance can be determined. THz radiation can be used to carry out the non-destructive testing and quality control of the materials and objects, including the analysis of tablets and pharmaceutical products during production for quality control purposes [15] [16]. This offers a marked improvement and advantage as compared to the other techniques like X-rays scanning and traces detection. Another example of non-destructing testing includes detecting and preventing smuggling of objects and illicit drugs across borders and countries.

#### 1.3.3 Spectroscopy

referred the interaction phenomenon Spectroscopy is to as between electromagnetic radiations and matter and it is used to carry out the measurement of intensity of radiation as function of wavelength. Examples of spectroscopic systems include (but are not limited to) near infrared, Raman, gamma and X-ray spectroscopy. In a spectroscopic system, it is possible to determine the electrical characteristics of the material by knowing the absorbance or reflectance of molecules of the detected signal [8] [14] [17]. The Time Domain Spectroscopy (TDS) works on the principle of coherent detection which determines the amplitude and phase of the received sample signal. The TDS is considered to be one of the most useful application fields of THz waves [18].

#### 1.3.4 Communications

Wireless data rates have drastically increased over the last decade for information sharing purposes because of which there has been a high demand for much higher speed wireless communication systems. THz systems can provide an option for extremely high data rate transmission for both the wired and wireless transmission since in THz range, high communication rates can be achieved with modulation techniques [19] [20] [21] . This possibility of THz-based communication can also alleviate the problems regarding spectrum scarcity and data limitations pertaining to the current wireless standards. However as discussed earlier, due to very low power levels of the THz sources and high water and atmospheric absorption, THz radiation is severely attenuated which necessitates the requirement for directive systems. Moreover this also puts a limit regarding the distance as THz based communication can be used for only short range or line-of-sight communication since the limiting factors hamper their potential for long range communication.

#### 1.3.5 Astronomy

One of the most fascinating applications of THz region is its usage to understand atmospheric composition, as well as the formation of planets and stars of the solar system [22] [4].The interstellar medium, which is considered to be the matter existing in space between stars and in galaxy consists of gases in various forms, dust particles and cosmic rays. It is an experimentally proven fact that 98% of the photons emitted by the Big Bang fall either in the infrared or THz band. The age of galaxies can therefore be estimated by determining the energy levels of these photons. Likewise, THz radiation can also be used to observe composition of the earth's outer hemisphere where atmospheric temperature generally varies between 10K up to several 100K temperature range as it helps in determining the behavior, pressure and concentration of the gases surrounding the earth atmosphere. These gases include nitrogen, oxygen, argon and carbon dioxide among others as well as the ozone layer that absorbs the harmful rays emitted by the sun. Observing ozone gas is also critical to monitor pollution and global warming [22].

### 1.4 THz Sources

In the THz gap, the difficulty for signal generation stems from the fact that solidstate electronic sources are limited by the maximum operating frequency of the device which is useful for RF and microwave regions but not for THz signal generation. Of late however, with the advancement in Si technology the device speed is pushing well into the lower end of THz region, making it possible to design low power sources [23] [24]. On the other hand, photon energy of many optical sources is very low at room temperature, rendering them ineligible to use in THz region. THz radiations can be generated using thermal, electronic and optical means [25]. In the next section, these sources are explained in more detail.

#### 1.4.1 Thermal Sources

Any radiating object operating at a temperature above absolute zero produces THz radiation. An example is a blackbody radiator which is a thermal based THz source having broadband characteristics that can radiate waves up to Infrared region. However, the emission efficiency of a blackbody radiator is low and the radiated power is only in nanowatt range.

#### 1.4.2 Electronic Sources

The electronic THz sources include:

#### 1.4.2.1 Backward Wave Oscillator (BWO)

A BWO is a vacuum tube that is used to generate waves in the microwave up to the THz frequency range [26]. Its principle of operation is based on the interaction of an electron beam with a slow wave structure. The BWO produces high power THz radiation, typically of the order of a few watts (W). The main disadvantage of the BWO is that it requires a strong magnetic field to operate and it is also potentially fragile.

#### 1.4.2.2 Gunn and IMPATT diodes

Gunn and IMPATT diodes are usually exploited in the microwave regime where they can be used as oscillators or amplifiers based on their negative conductance. They

are high power devices and have recently been implemented to produce THz waves at 0.7 THz signal frequency [27] [28]. However, their application in the THz frequencies is still in the preliminary stages of the research work and they are not used for commercial applications.

#### 1.4.2.3 Free electron laser

Free Electron Laser (FEL) is a high output power source capable of producing THz radiation. The principle of operation of a FEL is based on the acceleration of the free electrons through vacuum to a relativistic speed, and then decelerating these high speed electrons by moving them through a magnetic structure where they lose energy which is ultimately converted into light [29]. A FEL can generate power from several hundred of Watts (W) to kilowatts (kW). One advantage of the FEL is that its frequency can be fine-tuned continuously within 0.1 THz to 10 THz. However, the disadvantages include high cost, large and complex systems due to which the FEL based sources are only limited to scientific research area.

#### 1.4.2.4 Frequency Multipliers

Frequency multiplier is an example of Si based electronic source and it works on the principle of multiplication of the fundamental frequency to reach up to the THz frequency range. They make use of the Power Amplifier (PA) in the RF and microwave region, where enough transistor gain is available to provide the necessary RF power. The fundamental frequency is then passed through frequency doublers and triplers to reach the desired frequency [30] [24] . However, implementing the PA on-chip occupies area and consumes a lot of DC power. Despite of this, a lot of research activity in the recent past has focused on designing THz sources using frequency multipliers [31] [32].

#### 1.4.2.5 Oscillators

Si based oscillators provides another option to implement electronic THz sources. As the maximum oscillation frequency is limited and defined by the technology, harmonic oscillators can be utilized to increase the fundamental frequency in order to generate the desired signal in the THz range. A few examples of these oscillators are given in [33] [23].

#### 1.4.3 Optical Sources

Optical THz sources can be broadly divided into two categories:

- Continuous Wave (CW) sources

- Pulsed sources

The Quantum Cascade Lasers (QCL) and photomixers are good examples of CW THz sources, although they can also be used in pulsed-mode. These are described in detail in the following paragraphs.