## International Doctorate School in Information and Communication Technologies

## DISI - University of Trento

# Design and Analysis of Load-Balancing Switch with Finite Buffers and Variable Size Packets

Yury Audzevich

Advisor:

Prof. Yoram Ofek

Università degli Studi di Trento

Co-Advisor:

Prof. Renato Lo Cigno

Università degli Studi di Trento

December 2009

## Abstract

As the traffic volume on the Internet increases exponentially, so does the demand for fast switching of packets between asynchronous high-speed routers. Although the optical fiber can provide an extremely high capacity, the Internet switches still remain the main point of traffic bottleneck. The packet switching time may run up to nanoseconds in such routers with more than thousands ports, each processing at 10 GB/s. Even modern extremely fast processing units are not capable to satisfy these needs. It is well known that switching of such a high volume of traffic from input to output requires large buffers and fast processors to perform the header processing, complex scheduling and forwarding functions. Although a large number of switching architectures is presented on the market, the considerable part of them is either not scalable or reach their limits in power consumption and complexity. Therefore, novel and extremely scalable switching systems are essential to be investigated.

The load-balancing switching approach is simple, and therefore, may be capable of performing the switching and forwarding from all inputs to all outputs simultaneously with low complexity and high scalability. Since this simple approach has distributed topology (each component of the switch is controlled by an individual chip) and do not require fast switch control units, primarily because each stage is independent and it makes its own distributed calculations, it becomes a perfect candidate for the future practical deployment. The load-balancing switching architecture, considered in this thesis, is proved to have high potential to scale up while maintaining good throughput and other performance characteristics. Additionally, the load-balancing switching architecture can effectively resolve the important problem of packets mis-ordering which can appear due to the distributed structure of the system. Unfortunately, in the research conducted previously, some of the mentioned characteristics were obtained under a set of strong assumptions. In particular, it was assumed that all the packets transmitted through the system have equal length, traffic is admissible and central stage buffers are infinite. On the other hand, due to the distributed control the switch is not able to control and maintain a necessary amount of traffic transmitted from stage to stage inside the switch.

The following Ph.D. thesis analyzes behavior of the load-balancing switch equipped with finite central stage buffers. Due to this fact the LB switch will always have a possibility to drop a packet due to an overflow. In this work we first analyze the packet loss probability in the central stage buffers while considering packets of the same length (data cells). The analysis will be performed for both admissible and inadmissible traffic matrices. The obtained results show that the packet loss can have a significant influence on the overall LB switch performance if inputs of the switch are overloaded.

In order to present more realistic scenario, the packet loss analysis was performed in the switch with variable size packets. It is considered that most of the internet switches are operating on the cell-based level (to increase buffer utilization), that means that arriving variable size packets are segmented at inputs and reassembled at outputs. The issue of possible cell and correspondingly a packet loss inside the switch can introduce some significant posterior problems to the load-balancing switch reassembly unit. In order to evaluate packet loss we assumed Markovian behavior to be able to use numerically efficient algorithms to solve the model. The mathematical model characterizing inhomogeneous input traffic presented inside the thesis gives the most precise way of packet loss probability evaluation. Unfortunately, the high complexity of this model results in irresolvably complex Markov chains even in case of very small switches. Consequently, as a next step, we performed the analysis with fast solution procedures using a restrictive assumption of identical stochastic processes at all inputs. The final results allowed us to conclude that a single cell drop at the central stage buffers cause the whole packet removal and, the packet loss probability inside the system can be extremely high in comparison with the corresponding cell loss. Another important issue observed from the analysis is the difference in packet loss probabilities depending on the traffic traversing path, e.g. sequential number of input, central stage buffer and output of the switch. This property makes more complex the evaluation of the loss probabilities for large switch sizes. The last but not the least issue observed by our analysis was the instability, congestion and large delays appearing at output re-sequencing and reassembly unit due to the the central stage packet loss.

In order to cope with such a behavior, we proposed the novel algorithms which are able to efficiently minimize/avoid packet loss at the central stage buffers of the switch. For instance, the novel minimization protocol is introducing an artificial buffering threshold at the central stage buffers in such a way that packets at the input stage are are dropped in case the actual central stage buffers occupancy is above the threshold. The results show that due to possible packet removal at the input stage of the switch, the overall packet loss probability is significantly reduced. Similarly to the loss minimization service protocol, the novel NoLoss load-balancing switch operates while using information from both inputs and central stage buffers, and allows a packet transmission through the switch only if the central stage buffers have enough space to accept it during the current and the following time slots. In order to minimize communication overheads, the algorithm was implemented by means of centralize controller. Finally, such kind of management helped us to reach the lower boundary in the overall packet loss probability and resolve some other important issues of the switch, like, for instance, the congestion problem of the output reassembly unit.

### Keywords

[Scalable switch design, load-balancing switch, packets mis-ordering, cell loss, packet loss, congestion avoidance protocol, noloss switch]

## Acknowledgments

I am extremely grateful to my advisor Prof. Yoram Ofek for his incredible wisdom, immense knowledge, motivation and enthusiasm provided during my Ph.D. study in Italy. His guidance helped me in all the time of research, and his continuous support encourage me not only in professional but also in moral respect. I could not have imagined having a better advisor for my Ph.D. study.

Besides my advisor i would like to thank to my co-advisor Prof. Renato Lo Cigno, for his relentless support, supervision, advices and his continuous involvement into my research activities and assistance in resolution of non-scientific concerns. I am grateful in every possible way and hope to keep our collaboration in the future.

Many sincere thanks go in particular to Prof. Miklós Telek for his continuous help and guidance. I am really grateful to him for the offered opportunity of visiting and working with the members of the Stochastic Modelling lab at the Technical University of Budapest. Both Prof. Miklós Telek and all the members of his group have created inexhaustibly energizing, motivating and supportive atmosphere in the lab. My special thanks are dedicated to my friend and colleague Levente Bodrog for sharing his experience with me in stochastic modelling, his productive discussions and readiness to help.

Finally, i would like to express my sincere gratitude to Prof. Bűlent Yener without whom the investigations on the topic of this thesis might not even have been initiated. His experience, wise advices and assurance of success have enlightened me in the first glance of the research in the load-balancing switching field.

For all good time and support during my Ph.D. years I am grateful to my colleagues and friends, especially to: Danilo, Vladimir, Dmitry, Olga, Nikolay, Ivan, Andrey, Raman, Thang, Huong and Marcin.

Last but not the least, I would like to thank my family for their invaluable help and support: my parents, and my wife Tatsiana.

#### This work is dedicated...

To the memory of my departed uncles, grandparents and Yoram.

# **Contributions and publications**

This work has been developed in collaboration with various people and in particular with: Yoram Ofek, Renato Lo Cigno, Miklós Telek, Bűlent Yener, Levente Bodrog, Danilo Severina, and Giorgio Fontana.

This thesis makes the following contributions:

- Presents an overview of the currently deployed switching technologies on the market;

- Reviews the scalability limitations of the load-balancing switching architectures;

- Performs analysis of the load-balancing switching architectures with fixed and variable size packets;

- Presents mathematical models and simulator for the packet loss evaluation inside the switch;

- Proposes design and analysis of protocols which minimize/avoid the central stage packet loss of the load-balancing switch;

Part of the material of the thesis has been published (to appear) in various conferences, journals and technical reports (in order of appearance):

- [69]: Y.Audzevich, Y. Ofek, M. Telek and B. Yener. Analysis of Load-Balanced Switch with Finite Buffers. In *IEEE GLOBECOM' 08*, Dec. 2008.

- [6]: Y. Audzevich and Y. Ofek. Assessment and Open-issues of the Load-balanced Switching Architecture. In *IEEE FGCN'08*, Dec. 2008.

- [4]: Y. Audzevich, L. Bodrog, M. Telek, Y. Ofek, and B. Yener. Variable Size Packets Analysis in Load-Balanced Switch with Finite Buffers. In *Technical report*, *TU Budapest*, Apr 2009.

- [5]: Y. Audzevich, M. Corra, G. Fontana, Y. Ofek and D. Severina. Energy Efficient All-Optical SOA Switch for the Green Internet. In *FOTONICA'09*, May 2009.

- [3]: Y. Audzevich, L. Bodrog, Y. Ofek and M. Telek. Scalable model for packet loss analysis of Load-Balancing switches with identical input processes. In *IEEE ASMTA'09*, Jun 2009.

- [2]: Y. Audzevich, L. Bodrog, Y. Ofek and M. Telek. Packet Loss Analysis of Load-Balancing Switch with ON/OFF Input Processes. In *EPEW'09*, Jul 2009.

- Y. Audzevich and Y. Ofek. Overview and Evaluation of Load-Balancing Switches. Submitted to *Computer Networks* Journal.

- Y. Audzevich, L. Bodrog, Y. Ofek and M. Telek. Packet Loss Minimization in Load-Balancing Switch. Submitted to *IEEE ASMTA '10*.

- Y. Audzevich, G. De Blasio, R. Lo Cigno, M. G. Frecassetti, F. Granelli and D. Kliazovich. SoPSim: Simulation of Circuit Emulation over Packet for Microwave Radio Links. Submitted to *IEEE EuWiT '10*.

Whenever results of any of these works are reported, proper citations are made in the body of the thesis.

ii

# Contents

| 1        | Introduction |                                                     |                                                                    | 1        |

|----------|--------------|-----------------------------------------------------|--------------------------------------------------------------------|----------|

|          | 1.1          | The C                                               | ontext                                                             | 1        |

|          | 1.2          | Proble                                              | ems, Solutions and Thesis Structure                                | 3        |

| <b>2</b> | Stat         | te of tl                                            | ne Art and Related work                                            | <b>5</b> |

|          | 2.1          | Classif                                             | fication of Switching Architectures                                | 7        |

|          |              | 2.1.1                                               | Distributed designs with fix routes                                | 8        |

|          |              | 2.1.2                                               | Distributed designs with non-deterministic routes                  | 10       |

|          |              | 2.1.3                                               | Time-Driven switching                                              | 12       |

|          | 2.2          | The L                                               | oad-Balancing Switching Architecture                               | 12       |

|          |              | 2.2.1                                               | The architecture, assumptions and open issues                      | 13       |

|          | 2.3          | LB Sw                                               | vitch Designs Preventing Cells Mis-Sequencing                      | 17       |

|          |              | 2.3.1                                               | Uniform frame spreading                                            | 17       |

|          |              | 2.3.2                                               | Padded frame algorithms                                            | 18       |

|          |              | 2.3.3                                               | The mailbox switch                                                 | 18       |

|          |              | 2.3.4                                               | The Contention and Reservation switch                              | 20       |

|          |              | 2.3.5                                               | The Concurrent Matching switch                                     | 21       |

|          |              | 2.3.6                                               | Re-sequencing in the multi-stage buffering scheme                  | 22       |

|          |              | 2.3.7                                               | Byte-Focal switch                                                  | 23       |

|          | 2.4          | ation of the System's Scalability in Space and Time | 24                                                                 |          |

|          |              | 2.4.1                                               | Scalability limitations regarding the basic scheme                 | 24       |

|          |              | 2.4.2                                               | Scalability of recent architectures, computation and communication |          |

|          |              |                                                     | overhead                                                           | 25       |

| 3        | Scie         | entific (                                           | Questions                                                          | 35       |

|          | 3.1          | The C                                               | onsidered Open Issues                                              | 36       |

|          |              | 3.1.1                                               | Cell and packet loss                                               | 36       |

|          |              | 3.1.2                                               | Ways to avoid packet loss                                          | 38       |

|          |              | 3.1.3                                               | Re-sequencing and reassembly                                       | 39       |

|          | 3.2          | Future                                              | e Research Directions                                              | 40       |

| 4        | LBS                                | 5 with | Equal Size Packets                                                                                               | 41  |  |  |

|----------|------------------------------------|--------|------------------------------------------------------------------------------------------------------------------|-----|--|--|

|          | 4.1                                | The C  | Considered LBS Architecture                                                                                      | 41  |  |  |

|          | 4.2                                | Assum  | ption and Traffic Model                                                                                          | 42  |  |  |

|          | 4.3                                | The P  | acket Loss Analysis: 2 x 2 LBS case                                                                              | 43  |  |  |

|          | 4.4                                | The P  | acket Loss Analysis: N x N LBS case                                                                              | 46  |  |  |

|          | 4.5                                | Comp   | utational Results and Summary                                                                                    | 51  |  |  |

|          |                                    | 4.5.1  | Numerical and simulation model                                                                                   | 51  |  |  |

|          |                                    | 4.5.2  | Results and interpretations                                                                                      | 52  |  |  |

| <b>5</b> | The LBS with Variable Size Packets |        |                                                                                                                  |     |  |  |

|          | 5.1                                | The C  | Considered Load-Balancing Switching Architecture                                                                 | 59  |  |  |

|          | 5.2                                | The G  | eneral Case Packet Loss Analysis                                                                                 | 60  |  |  |

|          |                                    | 5.2.1  | Properties of the different paths                                                                                | 61  |  |  |

|          |                                    | 5.2.2  | The cell level model                                                                                             | 62  |  |  |

|          |                                    | 5.2.3  | The packet level model $\ldots$ | 65  |  |  |

|          |                                    | 5.2.4  | The probabilities of packet loss and successful packet transmission .                                            | 69  |  |  |

|          |                                    | 5.2.5  | Analysis of $N \times N$ load-balancing switch $\ldots \ldots \ldots \ldots \ldots \ldots$                       | 72  |  |  |

|          | 5.3                                | The O  | $O(2^N)$ Complexity Packet Loss Analysis                                                                         | 73  |  |  |

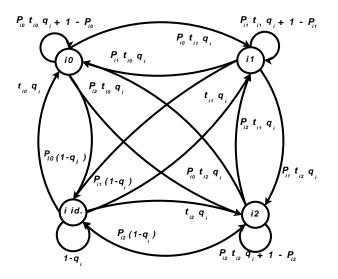

|          |                                    | 5.3.1  | Input model                                                                                                      | 73  |  |  |

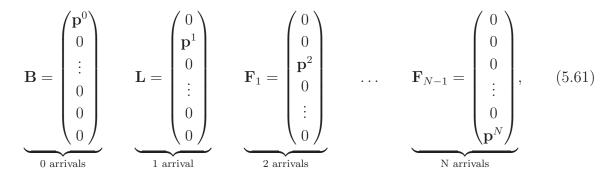

|          |                                    | 5.3.2  | The cell level model                                                                                             | 76  |  |  |

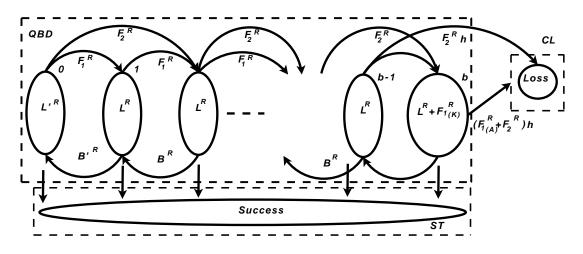

|          |                                    | 5.3.3  | The packet level model                                                                                           | 78  |  |  |

|          | 5.4                                | The L  | inear Complexity Packet Loss Analysis                                                                            | 82  |  |  |

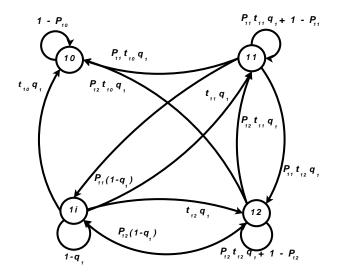

|          |                                    | 5.4.1  | The model of the input processes $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                       | 82  |  |  |

|          |                                    | 5.4.2  | Aggregate input model                                                                                            | 85  |  |  |

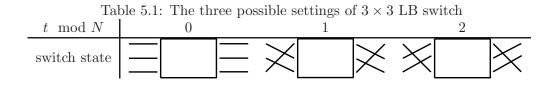

|          |                                    | 5.4.3  | The cell level model of the $3 \times 3$ switch $\ldots \ldots \ldots \ldots \ldots \ldots$                      | 86  |  |  |

|          |                                    | 5.4.4  | The packet level model $\ldots$ | 86  |  |  |

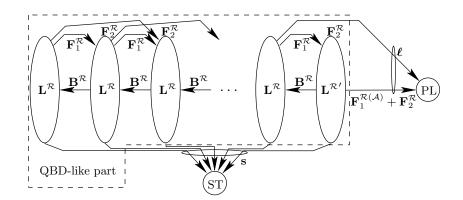

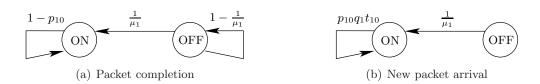

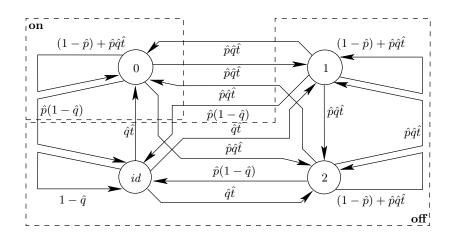

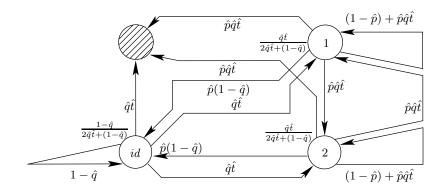

|          |                                    | 5.4.5  | On the solution of large QBD-like DTMCs                                                                          | 89  |  |  |

|          | 5.5                                | Exper  | imental Results and Summary                                                                                      | 90  |  |  |

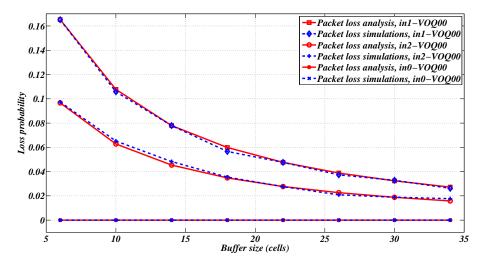

|          |                                    | 5.5.1  | Computation study: general case $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                        | 90  |  |  |

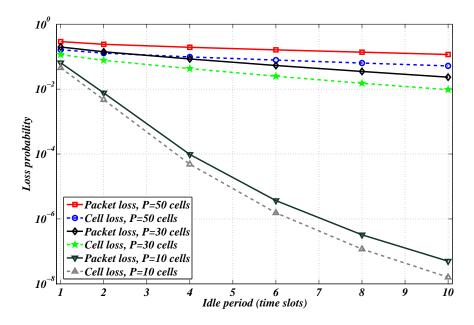

|          |                                    | 5.5.2  | Computation study: $2^N$ complexity case                                                                         | 93  |  |  |

|          |                                    | 5.5.3  | Computation study: $N + 1$ complexity case $\ldots \ldots \ldots \ldots \ldots$                                  | 94  |  |  |

|          |                                    | 5.5.4  | Additional simulation results                                                                                    | 97  |  |  |

|          |                                    | 5.5.5  | Summary                                                                                                          | 104 |  |  |

| 6        | Pac                                | ket Lo | ss Minimization and Avoidance                                                                                    | 107 |  |  |

|          | 6.1                                | Protoc | col for Packet Loss Minimization                                                                                 | 108 |  |  |

|          |                                    | 6.1.1  | The Implementation $\ldots \ldots \ldots$  | 108 |  |  |

|          |                                    | 6.1.2  | Information exchange in the controller                                                                           | 111 |  |  |

|          |                                    | 6.1.3  | LB switch overheads and scalability                                                                              | 113 |  |  |

|          |                                    |        |                                                                                                                  |     |  |  |

|              |       | 6.1.4   | 5.1.4 The Packet Loss Analysis $\ldots \ldots 114$ |       |  |

|--------------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|--|

|              |       | 6.1.5   | Differences in the cell level model                                                                                                           | . 115 |  |

|              |       | 6.1.6   | The packet level model                                                                                                                        | . 115 |  |

|              |       | 6.1.7   | The initial distribution of the packet level model                                                                                            | . 116 |  |

|              |       | 6.1.8   | The minimal loss probability of the system                                                                                                    | . 117 |  |

|              |       | 6.1.9   | Experimental results                                                                                                                          | . 117 |  |

|              |       | 6.1.10  | Summary                                                                                                                                       | . 120 |  |

|              | 6.2   | NoLos   | s Load-Balancing Switch                                                                                                                       | . 120 |  |

|              |       | 6.2.1   | The architecture                                                                                                                              | . 122 |  |

|              |       | 6.2.2   | Experimental results                                                                                                                          | . 129 |  |

|              |       | 6.2.3   | Summary                                                                                                                                       | . 133 |  |

| 7            | Con   | clusior | 1                                                                                                                                             | 135   |  |

|              | 7.1   | Summa   | ary                                                                                                                                           | . 136 |  |

|              | 7.2   |         | Work                                                                                                                                          |       |  |

| Bi           | bliog | graphy  |                                                                                                                                               | 139   |  |

| $\mathbf{A}$ | Acr   | onyms   |                                                                                                                                               | 145   |  |

# List of Tables

| 2.1 | Potentially scalable switching architectures                                                                                                                                                 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1 | LB switch occupancy during three time slots                                                                                                                                                  |

| 4.2 | Possible variation of the function values versus arrival probabilities 45                                                                                                                    |

| 5.1 | The three possible settings of $3 \times 3$ LB switch $\ldots \ldots \ldots$ |

| 5.2 | The possible time evolution of input 1 with packet arrival                                                                                                                                   |

| 5.3 | Parameters used for the numerical studies                                                                                                                                                    |

| 5.4 | The main parameters of the computation                                                                                                                                                       |

| 5.5 | Parameters used for the numerical studies                                                                                                                                                    |

| 5.6 | Parameters used for simulations of Part 1                                                                                                                                                    |

| 5.7 | Parameters used for simulations of Part 2                                                                                                                                                    |

| 5.8 | Parameters of used Pareto distribution                                                                                                                                                       |

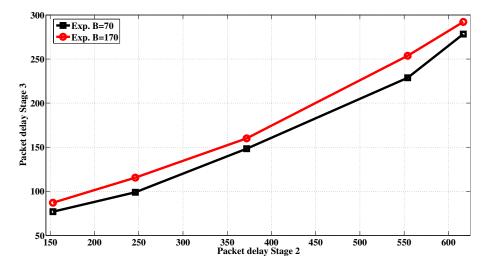

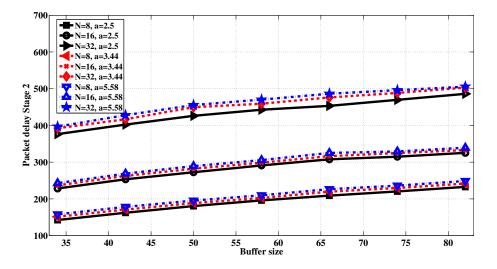

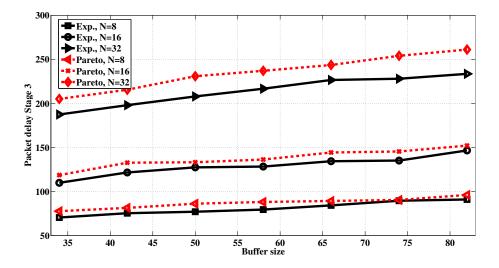

| 5.9 | Packet delay grows analyzed in Figure 5.30                                                                                                                                                   |

| 6.1 | Total system overheads for various implementation schemes                                                                                                                                    |

| 6.2 | Parameters used for the numerical studies                                                                                                                                                    |

| 6.3 | Parameters used for the simulations                                                                                                                                                          |

# List of Figures

| Parallel Iterative Matching: one iteration                                                        | 9                                          |  |  |

|---------------------------------------------------------------------------------------------------|--------------------------------------------|--|--|

| Representation of iSLIP matching algorithm                                                        | 9                                          |  |  |

| The basic LB switch                                                                               |                                            |  |  |

| Tree embedded ring; short-cut $(VN_2 - VN_4)$ and jump $(C - G)$                                  | 11                                         |  |  |

| Use of single input buffer switch for Hot-potato, MSN and MetaNet routing                         | 12                                         |  |  |

| LB switch with single-stage buffering                                                             | 13                                         |  |  |

| The Mailbox switching architecture [15]                                                           | 19                                         |  |  |

| Example of symmetric interconnection pattern [15]                                                 | 19                                         |  |  |

| The Contention and Reservation switch $[75]$                                                      | 20                                         |  |  |

| The Concurrent Matching switch [46]                                                               | 21                                         |  |  |

| LB switch with multi-stage buffering [18]                                                         | 22                                         |  |  |

| The Byte-Focal switch $[57]$                                                                      | 23                                         |  |  |

| The Frame-Aggregated CM switching architecture [47]                                               | 30                                         |  |  |

| Staggered symmetry interconnection pattern for $N = 3$ [73]                                       | 32                                         |  |  |

| The considered LB switching architecture                                                          | 36                                         |  |  |

| Single-stage buffering LB switch                                                                  | 42                                         |  |  |

| 2 x 2 LB switch                                                                                   | 44                                         |  |  |

| State-transition diagram for $2x2$ LB switch with central buffer of size $B = 4$                  | 45                                         |  |  |

| N x N LB switch with finite buffers $\ldots$                                                      | 47                                         |  |  |

| Possible transitions of $N \times N$ LB switch when $B > i - 1 + N$                               | 48                                         |  |  |

| The transition graph of LB switch with $N = 3$ and $B = 5$                                        | 50                                         |  |  |

| The transition probability matrix $Q$                                                             | 50                                         |  |  |

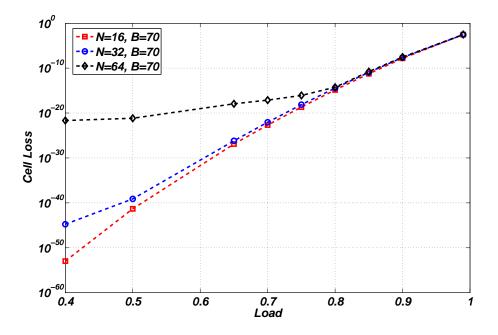

| Cell loss versus load ( $\rho = 0.40.99$ ) for N x N LB switch, buffer=70 cells,                  |                                            |  |  |

| admissible uniform i.i.d traffic                                                                  | 52                                         |  |  |

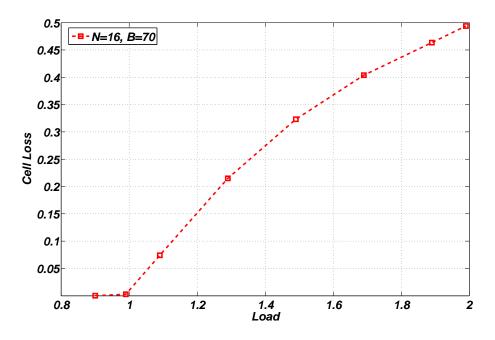

| System loss versus load for N x N LB switch, overall load range $\rho$ =                          |                                            |  |  |

| $0.91.99$ , buffer = 70 cells, inadmissible traffic. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 53                                         |  |  |

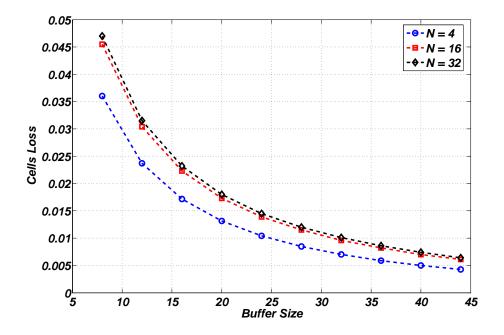

| Cell loss versus buffer size, overall load 0.99, admissible uniform i.i.d traffic.                | 54                                         |  |  |

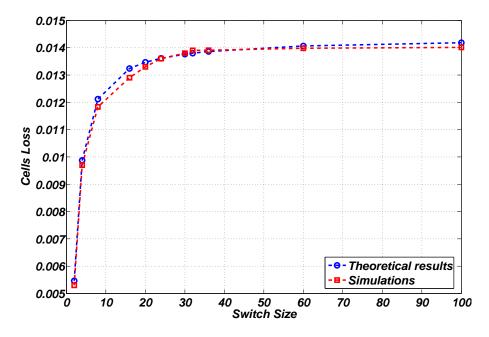

| Cell loss versus switch size, overall load $0.99$ , buffer size = 25 cells, admis-                |                                            |  |  |

| sible uniform i.i.d traffic.                                                                      | 54                                         |  |  |

|                                                                                                   | Representation of iSLIP matching algorithm |  |  |

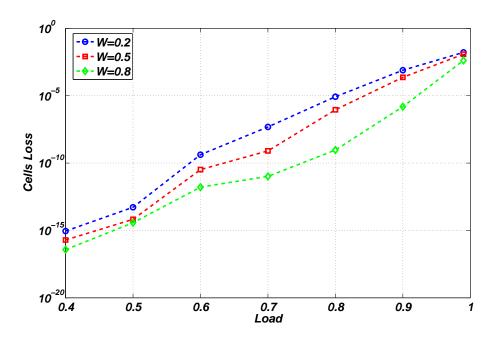

| 4.12 | Cell loss versus load, 16 x 16 LB switch, buffer size = 20 cells, admissible unbalanced i.i.d traffic, for different $W$ .                 | 55  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

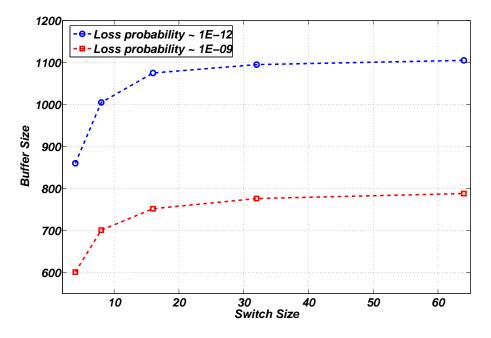

| 4.13 | Buffer size versus switch size with loss probability $1E - 12$ and $1E - 09$ , for overall load of 0.99 (admissible uniform i.i.d traffic) | 55  |

| 5.1  | The considered LB switch                                                                                                                   | 59  |

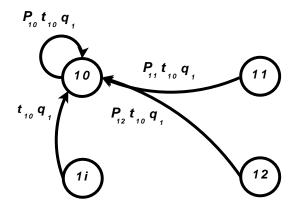

| 5.2  | The DTMC modeling input i                                                                                                                  | 63  |

| 5.3  | The transient DTMC for packet level model                                                                                                  | 66  |

| 5.4  | The revised DTMC model of input 1                                                                                                          | 67  |

| 5.5  | The DTMC of input 1; a new packet arrival                                                                                                  | 71  |

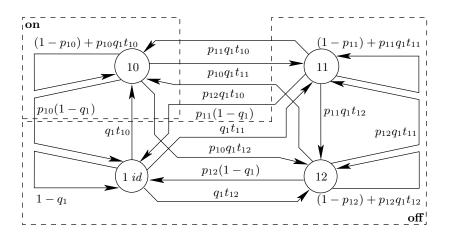

| 5.6  | The DTMC which fully characterizes input 1 of $3 \times 3$ LB switch                                                                       | 74  |

| 5.7  | The DPH substitution of <b>off</b> states for a pair with input 1 - output 0 $\ldots$                                                      | 75  |

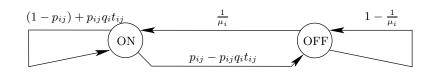

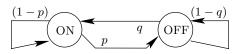

| 5.8  | The ON/OFF DTMC describing a pair with input $i$ - output $j$                                                                              | 76  |

| 5.9  | The transient DTMC which characterizes a VOQ during a life cycle of a                                                                      |     |

|      | packet                                                                                                                                     | 78  |

| 5.10 | The modified graphs of the ON/OFF DTMC describing input 1 $\ldots$ .                                                                       | 80  |

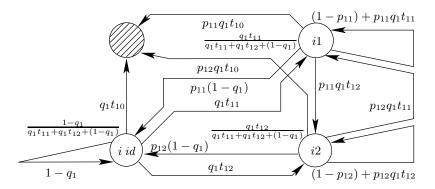

| 5.11 | The DTMC which characterizes every input of $3 \times 3$ LB switch $\ldots$ .                                                              | 83  |

| 5.12 | The DPH substitution of <b>off</b> states in terms of output $0 \ldots \ldots \ldots \ldots$                                               | 84  |

| 5.13 | ON/OFF model of the input process with a simplified notation                                                                               | 85  |

| 5.14 | Packet loss as a function of buffer size; comparison between analysis and                                                                  |     |

|      | simulations                                                                                                                                | 91  |

| 5.15 | Packet/cell loss of a specified path as a function of idle period $\ . \ . \ . \ .$                                                        | 92  |

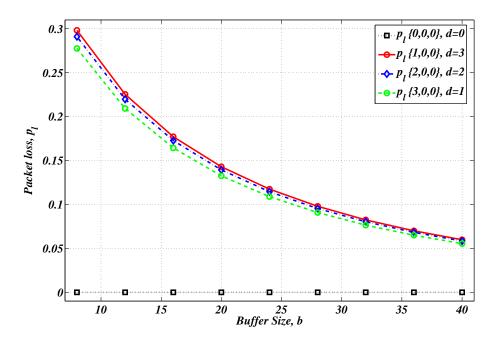

| 5.16 | Packet loss probability versus buffer size (study 1)                                                                                       | 94  |

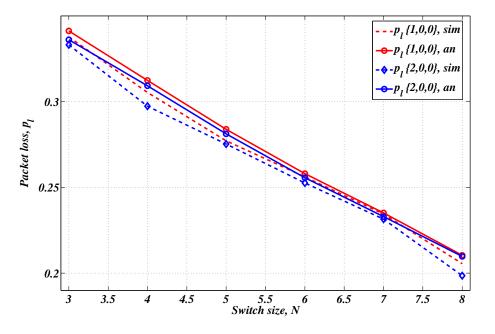

| 5.17 | Packet loss probability versus switch size (study 2) $\ldots \ldots \ldots \ldots$                                                         | 94  |

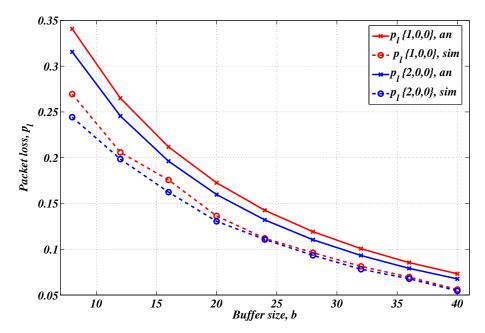

| 5.18 | Packet loss versus buffer size                                                                                                             | 95  |

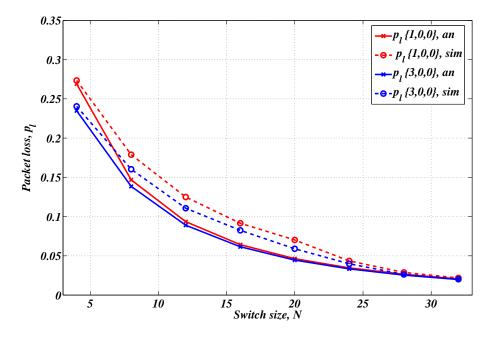

| 5.19 | Packet loss versus switch size                                                                                                             | 96  |

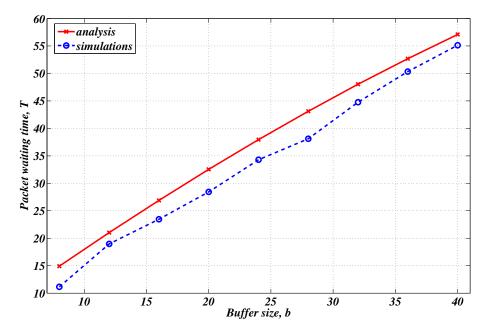

| 5.20 | Packet waiting time versus buffer size                                                                                                     | 96  |

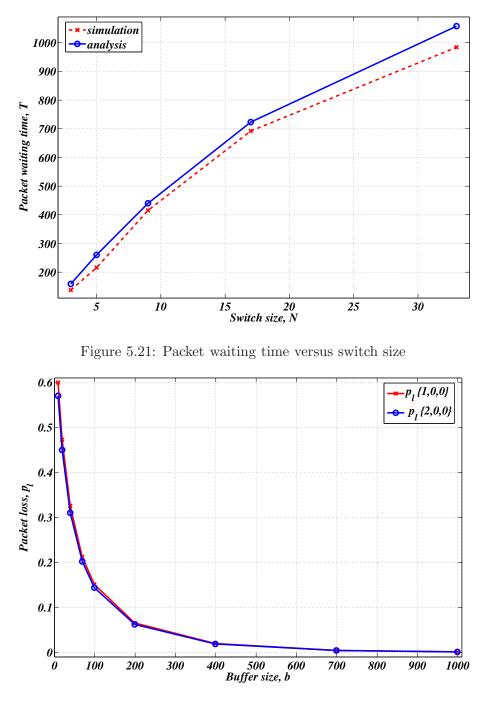

| 5.21 | Packet waiting time versus switch size                                                                                                     | 97  |

| 5.22 | Packet loss as a function of buffer size                                                                                                   | 97  |

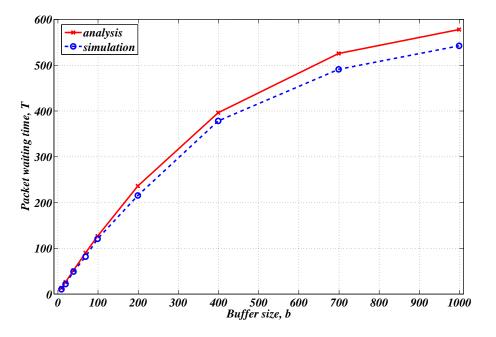

| 5.23 | Packet waiting time versus buffer size                                                                                                     | 98  |

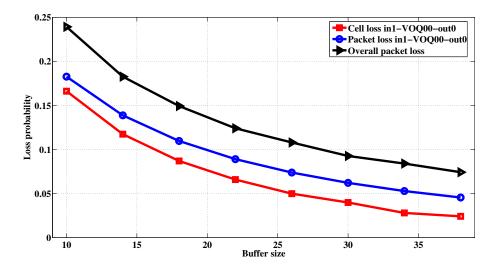

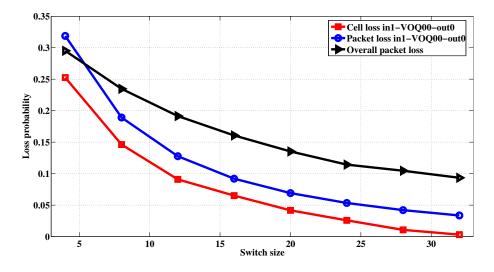

| 5.24 | Dependence of the overall packet loss, packet loss on a path and cell loss versus buffer size                                              | 99  |

| 5.25 | Dependence of the overall packet loss, packet loss on a path and cell loss                                                                 |     |

|      | versus switch size                                                                                                                         | 100 |

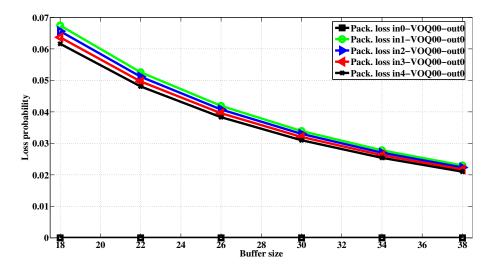

| 5.26 | Dependence of packet loss inside a path over buffer size                                                                                   | 100 |

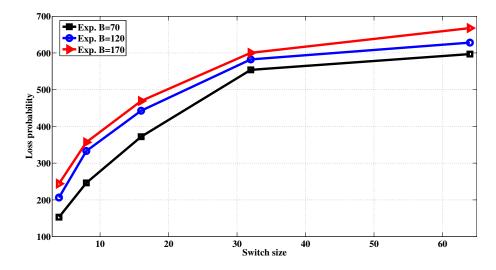

|      | Dependence of average packet traversing delay at the second stage versus                                                                   |     |

|      | switch size                                                                                                                                | 101 |

| 5.28 | Average packet delay at the output stage as a function of central stage                                                                    |     |

|      | packet delay                                                                                                                               | 102 |

| 5.29 | 9 Packet delay stage2 versus buffer size, average packet size 40 cells, interar-                                                                                                            |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|      | rival period 4 cells                                                                                                                                                                        |  |  |

| 5.30 | Dependence of packet reassembly delay on buffer size                                                                                                                                        |  |  |

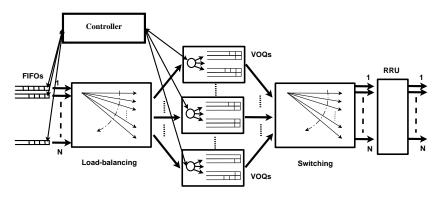

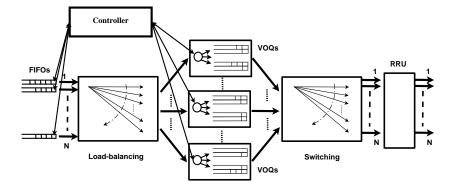

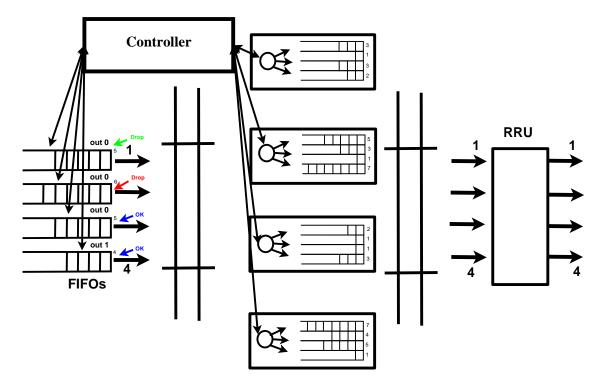

| 6.1  | The considered LB switch                                                                                                                                                                    |  |  |

|      |                                                                                                                                                                                             |  |  |

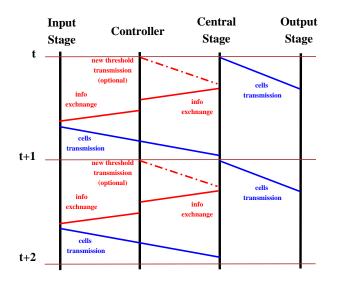

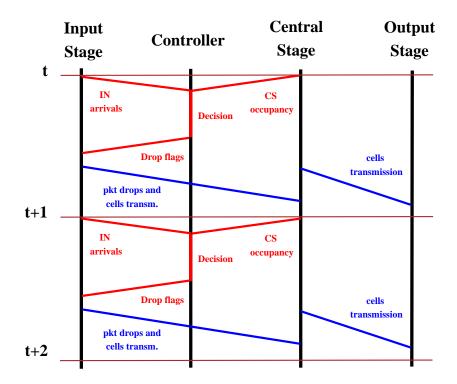

| 6.2  | Timing diagram                                                                                                                                                                              |  |  |

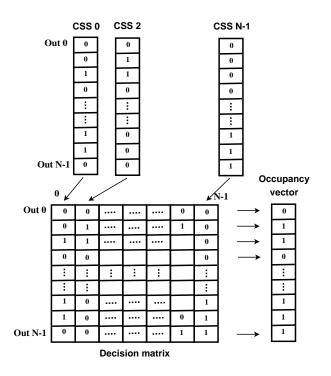

| 6.3  | Information processing and exchange at the centralized controller 112                                                                                                                       |  |  |

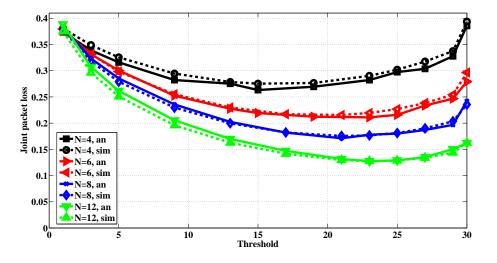

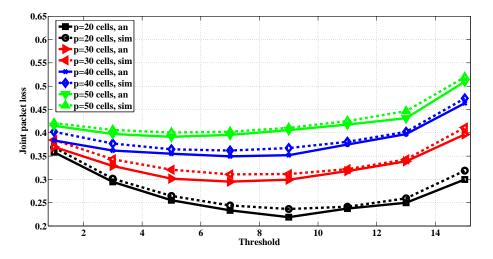

| 6.4  | Analytical and simulations representation of joint packet loss probability                                                                                                                  |  |  |

|      | versus threshold                                                                                                                                                                            |  |  |

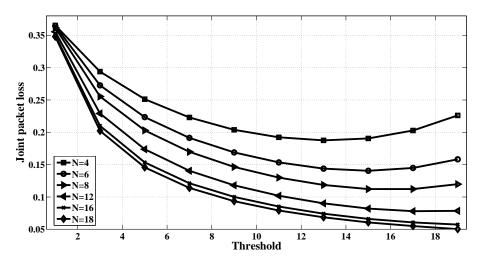

| 6.5  | Dependence of joint packet loss probability versus threshold for various                                                                                                                    |  |  |

|      | switch sizes                                                                                                                                                                                |  |  |

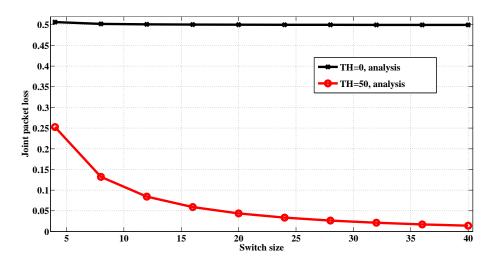

| 6.6  | Joint packet loss probability versus switch size                                                                                                                                            |  |  |

| 6.7  | Joint packet loss probability as a function of protocol threshold $\ . \ . \ . \ . \ . \ 120$                                                                                               |  |  |

| 6.8  | The NoLoss LB switching architecture                                                                                                                                                        |  |  |

| 6.9  | Example of $4 \times 4$ NoLoss LB switch                                                                                                                                                    |  |  |

| 6.10 | Sequence of controller operations during a time slot $\ldots \ldots \ldots$ |  |  |

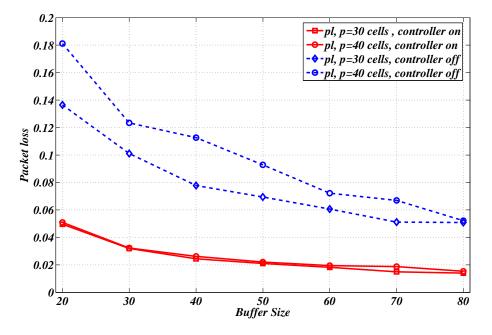

| 6.11 | Dependence of joint packet loss as function of buffer size $\ldots \ldots \ldots \ldots 130$                                                                                                |  |  |

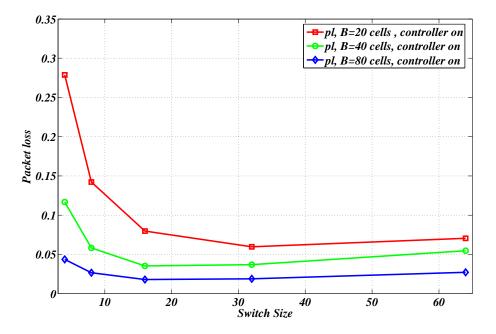

| 6.12 | Joint packet loss dependence versus switch size                                                                                                                                             |  |  |

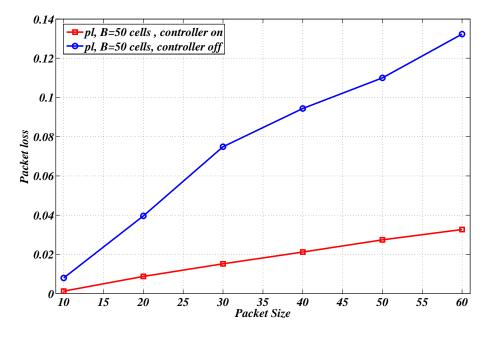

| 6.13 | Joint packet loss as a function of packet size                                                                                                                                              |  |  |

## Chapter 1

## Introduction

According to the latest statistics, the amount of users connected to the Internet is growing extremely fast every year. For instance, the World Internet Usage Statistics organization reports that during the period from 1992, when Internet was pulled to the general public, up to the present time the number of Internet users became 100 times larger. In addition to that, demand on the "bandwidth-hungry" applications is increasing every year. Various types of applications represented in the modern network cover all the aspects of human life. In particular, the network resources are widely used in business, science, and mostly at entertainment. The number of internet users can be easily divided in both the regard to the time spent online and the amount/type of applications they use. Technological developments in both the electronics and telecommunications have extended broadband capacity of private networks from a limited "Internet browsing" function to a fundamental entertainment capabilities while exploring services such as Video-on-Demand and IPTV.

#### 1.1 The Context

In order to provide the increasing demand to the network resources novel technologies for realization of transmission medium as well as for the Internet routing are introduced.

In spite of the cabling costs, the optical fiber is still remain the fastest and most reliable medium for data transmission. The situation is completely opposite with regard to the the Internet switching/routing. The traditional ways of packet switching are designed to connect multiple area networks (LANs, WANs, etc.) and forward asynchronous traffic between the communication links by means of routing protocols. Usually the transmission decision is evaluated by means of centralized controller, which is not considered to be a scalable solution for switch sizes of at least 1000 ports. Moreover, in order to maintain operating such an architecture, a considerable financial (extremely high power consumption [43]) and administrative (by involving network administrators) investments should be constantly done. In this context, switches with distributed control are looking more attractive. In such a system, the packet scheduling decision is achieved by a separate block which is independent from all other system's blocks. Although the on-chip control is not always considered to be simple, it gives the possibility to easily scale up the system without significant drop in performance.

In this thesis we focus on the representation of the various switching/routing architectures based on the distributed control. The initial part of this thesis, e.g. chapter 2, will show the technologies used for a scalable switch/router implementation. The main task of each network router can be simply reduced to routing and forwarding of incoming information. It is considered that a router is operating in both control plane (the process of the most optimal interconnection decision is performed) and forwarding plane (where the information is actually sent). However, it is possible that due to internal router topology, the complete routing decision cannot be specified at the control plane at once. This rule is mostly related to the routers implementing non-deterministic or adaptive forwarding. In contrast to the assignment of a fixed traversing route, such routers can dynamically decide which hop(s) is(are) more preferable for optimal information forwarding. The main drawback of routers with non-deterministic routing can be the capacity expensive communication overheads, which in some cases can be even larger than the amount of information transmitted. Additionally, such routers are a subject of extremely large traversing delays and low throughput.

In contrast, the forwarding decision which is performed in distributed routers with deterministic management can be specified after a decision making phase. The loadbalancing (LB) switch can be attributed to such a category of routers. It was firstly presented in [16, 17, 40] where it is implementing extremely simple ingress-egress interconnection scheme, realized in round-robin run of crossbars. In general LB switch is composed of three stages, each of the stages contains a certain amount of buffering. The interconnection between the stages is performed by means of crossbar switches which are synchronized to the rest of the system. Due to the fact that decision about packet forwarding is deterministic at each time point, the system does not use any additional overheads for the forwarding decision phase. All these features deploy both extremely high scalability and good performance characteristics of the LB switch. All the positive features as well as novelty of the proposed approach makes the LB switch the main focusing point of this thesis.

The initial research on the topic of load-balancing was tackling only specific set of problems under the predefined set of assumptions (described also in section 2.2). Among the first significant results shown in [17] and [18] was the fact that under certain assumptions the switch can achieve high throughput (up to 100%) and low packet traversing delay. However these results were obtained under consideration that all the packets have equal length, traffic is admissible and central stage buffers are infinite. On the other hand, the important issue of packets mis-ordering was investigated into details

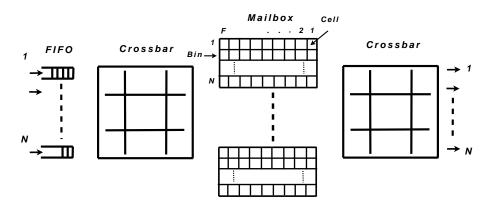

in [15, 40, 46, 57, 75]. It is important to mention that some of the architectures to resolve packets mis-sequencing require extra control, introducing different overheads (communication and computational), that basically increases the control complexity of the LB switch. However, keeping correct sequence of packets through the system avoids unnecessary retransmissions of packets in the network protocol layer [10].

#### **1.2** Problems, Solutions and Thesis Structure

The initially considered set of assumptions makes impossible to analyze the LB switch behavior under conditions existing in the real Internet router [23]. In particular the maximum system's throughput (100%) can be reached only in the ideal case with infinite central stage buffers. Taking into account the fact that practical networking devices will always have a limited space for packet storage and forwarding, in the future we perform analysis only for LB switches with finite amount of buffering (Chapter 3).

The first attempt to analyze (by means of simulations) the central stage packet loss was performed in [65]. In contrast to this work we propose in [69] a novel mathematical model, which allows to evaluate central stage packet loss for any set of parameters N- switch size, B - buffer size and traffic matrix A - which is also called an arrival rate matrix. The results of packet loss evaluation as well as the model itself will be presented in chapter 4. The first attempt of packet loss probability evaluation had one significant drawback. Throughout the paper [69] we assumed that all the packets arriving to the inputs are of the same size (also named as data cells). It is well known that due to a large variety of online applications, the Internet traffic is transporting packets with variable length. In order to transmit such a packet through a standard Internet switch arriving packets are segmented into a fixed size data cells at ingress ports and reassembled at egress ports after cell-by-cell forwarding. Holding this assumption for the LB switch we have performed the analysis of the packet loss probability with the assumption of variable size packets [4]. The mathematical model presented in chapter 5 section 5.2 shows extremely high complexity of given analysis. Since the LB switch itself is considered to be a highly scalable architecture, it is quite important to yield solution which is capable to converge extremely fast for large switch sizes and have a good precision. In order to satisfy these needs and simplify the mathematical model, some restrictive assumptions were applied to the arriving traffic. In particular we assumed the identical behavior, e.g. identically distributed arriving traffic, of all inputs. As a result the final complexity of the method was described as O(N+1) (chapter 5 section 5.4), which allowed us to perform evaluations for switches with large number of ports. The obtained mathematical model allowed us to evaluate packet loss probabilities for various packet and interpacket lengths. It was shown by results that the packet loss of the switch is always higher than the corresponding cell loss. This can be explained by the fact that a single cell drop is causing the whole packet

removal.

In addition to the mathematical model, as a tool to better understand and optimize performance and/or reliability of the LB switch, the LB switch simulator was also extensively used. In contrast to the modelling, the simulation tool allowed to explore obtained results and get understanding of the future behavior of the system when conditions close to real, e.g. heavy-tailed traffic matrices or limited amount of buffering at the output, are applied (like it is presented in section 5.5.4).

In addition to the problem of cell and packet loss at the central stage buffers, the analysis reveals a set of novel issues related to the re-sequencing and reassembly units (RRU). In particular, the amount of memory resources at RRU that can be held by congested data cells is expanding with increase of the central stage packet loss. Due to the fact that the LB switch does not perform any control on the traffic transmitted form a stage to another one, the data cells of incomplete packets (dropped at the central stage) arrive to outputs and should be handled by the processor of RRU. As a result of such unreliable packet transmissions a certain number of memory locations in the buffer is wasted by the cells of incomplete packets waiting for reassembly.

To resolve the system instability caused at RRU a set of novel protocols for the LB switch was proposed (see chapter 6). In order to reduce buffers capacity wastage produced by the central stage buffers congestion, it is preferable to predict a possible packet drop in inputs in order to remove it as a complete unit. Two types of algorithms were proposed to resolve this issue. The packet loss minimization service protocol, in section 6.1, bounds the amount of traffic transmitted from inputs to central stage while positioning a virtual threshold in central stage queues. This countermeasure, although, does not avoid central stage packet loss completely, but allows to reduce the amount of incomplete packets in the system. The second approach presented in section 6.2, in contrast, implements a management scheme which completely avoids central stage packet loss. Due to this fact, the overall packet loss of the system is always lower than in the traditional system. Finally these solutions allow to allocate the amount of buffering resources at each stage in order to perform the efficient reassembly process.

## Chapter 2

## State of the Art and Related work

Internet represents a complex topology asynchronous network of a very large numbers of queues that is continuously expanding in size and capacity. IP routers should be periodically upgraded to support the growing Internet capacity, enlarging exponentially every 18 month [40]. None of the recently operating single stage routers is capable of sustaining thousands of operational ports with simple control mechanism. Incoming asynchronous packets require fast routing processors and large buffering structures in order to lookup header [11] and hastily make fast output transmission decision. The forwarding table, that is stored in processor unit, looks for destination entries that best matches the destination network address of the packet. Practically, the router operating at high speeds are capable of performing millions of lookups per second. For routers of our interest, with size more than thousands ports, and supporting at least 10 GB/s per port rate, the packet switching time value may run up to nanoseconds [45]. Even the super fast processors are not capable to satisfy these needs. It is accepted estimation that single stage routers almost reach their capacity, and cannot scale up to the large sizes. Routers with distributed control [68] are meeting the requirements of designing a new scalable router. Usually distributed routers do not require relatively fast processing units [33] because each stage is independent and it makes its own self-calculations. Eventually, some disadvantages are highlighted on the use of distributed switching systems, and some of these problems may introduce significant changes in the operation stability. Some of the proposed solutions require more complex interactions with these distributed switches that can particularly affect the system scalability. As a result, we reveal the fact that not all distributed schemes are yet scalable and suitable for real Internet conditions support. One of the major motivations of this chapter is to analyze the distributed architectures represented so far in literature. This chapter aims at providing a comprehensive analysis of the switching architectures and main concepts behind switching architectures common to all switch vendors. The chapter begins by looking at most popular switching solutions and representation of their mechanisms to switch data. Then, we chose the most scalable solutions capable to provide good performance characteristics in real networks.

To start the discussion we refer to output buffer switches [36], which, at the moment are not of the great interest from the scalability prospectives. In spite of the fact, that switch is able to provide guaranteed throughput, the use of large memory speedup makes it non realizable for more than hundred of ports. Completely another interest is raised by input buffer switches where some scheduling decision algorithms are performed. To eliminate head-of-line blocking in the inputs, buffers with random access and virtual output queuing [36] structures get under the way. Apparently, input buffer switch requires scheduling algorithm in order to match and interconnect inputs with outputs. It is well known that both centralize controller or a distributed management schemes can be used to resolve ingress-egress matching problem. As our interest is given mostly to distributedcontrol algorithms (e.g. operating on per-port basis), next, we will present two particular implementations on the example of Parallel Iterative Matching (PIM) [62] and iSLIP [49] algorithms. We concentrate our attention on the input buffer switch defining two main implementation branches. The input buffer switches with fix routing schemes (like PIM and iSLIP) will be described first. However, the significant interest will be given also to representation of schemes with non-deterministic packet routing like presented in [8, 48,54, 55].

As a completely different approach, the Time-driven switching (TDS) [7] deploys pipeline forwarding inside the network using global common time reference. Thanks to coordinated universal time, all the switches in the network are synchronized and use negligible amount of buffering for packet transmission. TDS scheduler reserves transmission resources for a dataflow in advance, thus allowing packet header processing to be excluded.

The remaining part of the thesis, is dedicated to the novel LB switching architecture recently appeared in the research [32]. The careful attention is devoted to the fact that the LB switching architectures are considered to be highly scalable, have a simple distributed control and almost no scheduling overheads. Our goal is to present a different perspective on load-balancing switches, while considering their advantages and drawbacks. In spite of the fact that quite large number of publications was presented on the topic, in this chapter we introduce several new issues which were not mentioned previously. In the following, we first show initial LB switching architecture with the basic assumptions and main disadvantages. Next we shortly list the most crucial drawbacks related to the LB switching architecture. Among these, we focus on the most important issues like system scalability and packets mis-sequencing. Additionally, we analyze how this two issues are influencing one another and can be maintained all together in the appropriate level. We merge all available solutions for packets mis-sequencing into a single section with extra descriptions on the proposed solutions. In the section devoted to the systems' scalability analysis we evaluated computation and communication overheads which can appear in the proposed designs. In addition, we introduce a novel problem of cell/packet loss inside the switch. This issue has strong dependency on the system stability and its performance.

### 2.1 Classification of Switching Architectures

By definition, a network switch is considered to be a device that performs transparent ingress-egress bridging at up to speeds of a hardware. Topologically each switch can be viewed as a network located in a box. All the systems making internal switching can be further classified as input or output buffered depending upon the position of buffers. As it was mentioned before, our main requirements are to find switching architectures being capable of scaling up to at least of thousands ports and support of minimum 10 Gb/s per port rate.

Although a switch using output queuing has better throughput and delay performance characteristics than switches using input queuing, the hardware costs can be enormous for large output buffer switches. Moreover, output buffer switches are fairly complex and require large speedups of transmission buffers due to simultaneous arrival of more than one input packet for the same output [36]. On the other hand, it has been also shown that the throughput of a switch with input queuing is only 0.586 of the full capacity. The main reason of this poor throughput is due to head of line (HOL) blocking where packets at the head of input queues contend for the same output while the packets destined for free outputs are waiting in a line. Due to the implementation simplicity and total costs, it is still feasible to build large switches using input buffering techniques. Some ingenious solutions were proposed to solve HOL blocking problem [50].

In particular, instead of using first-in-first-out (FIFO) policy in each input the virtual output queuing (VOQ) scheme creates per output queues at each input. In such a way each packet occupies a virtual queue corresponding to the output, and none of the packets are blocked. Moreover, input buffer switch requires common scheduler. In practice, scheduler's complexity is in the strict relation with the system performance. Henceforward, our attention will be dedicated to algorithms distributing decision complexity among the ports, allowing the neglect of centralized control for an input buffered switch. In the following sections we will represent also the load-balancing [17, 18, 40] and Time-Driven [7] switching principles. In the upshot, some relevant to this thesis architectures, like Metaring [21] and MetaNet [54, 55] and, switching architectures build upon Combinatorial Designs [71, 72], will be depicted. Table 2.1 presents the classification of the most space-time scalability appropriate solutions in the research.

The Internet routers are making their routing decisions based on the knowledge of the network's topology and it's conditions. In a simple configuration, fixed or adaptive routing schemes are possible. Further, we will apply these principles of fix and nondeterministic routing for the "internal network-based" routers of the input buffer switch.

| Space     Time  | Sending over predefined routes    | Sending over non-<br>deterministic routes |

|-----------------|-----------------------------------|-------------------------------------------|

| Schedule        | Time-Driven Switching [7]         | NOT practical                             |

|                 | (Small memory, Connection ori-    |                                           |

|                 | ented, good for streaming media   |                                           |

|                 | support)                          |                                           |

| Without routing | input buffer switches with:       | Single input buffer switches              |

| schedule        | 1) PIM [62],                      | with placed "in a box" ap-                |

|                 | 2) iSLIP [49],                    | proaches of:                              |

|                 | 3) Load-Balancing switching [17,  | 1) Hot-potato Routing [8],                |

|                 | [18, 30, 39]                      | 2) Deflection Routing [48],               |

|                 | (Large memory, low loss, long de- | 3) MetaNet and Convergence                |

|                 | lay).                             | Routing [54, 55, 71, 72].                 |

Table 2.1: Potentially scalable switching architectures

A packet transferring with predefined route can be possible in the routers with schedulers or in the systems where predefined configuration is applicable. On the other hand, the architectures where packet traverses along a non-deterministic route can be present. Deflection routing [48] and MetaNet Convergence routing [54, 55], if to be positioned "in a box", can be a good example of a non-deterministic routing. Figure 2.5 shows the use of Hot-potato routing [8] and all the other non-deterministic routing-schemes located into a single input buffer router. Table 2.1 strictly differentiates and underline importance of these two routing approaches.

### 2.1.1 Distributed designs with fix routes

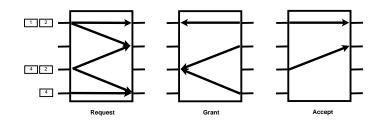

**Parallel Iterative Matching** [62]. The following matching algorithm was implemented in Input buffering switch, using memory with random access [62]. The algorithm finds conflict-free pairing of inputs to outputs, only for pairs with a queued cell to transmit between them. Parallel iterative matching uses parallelism, randomness, and iteration to accomplish matching efficiently. The operational steps during one iteration are the following (Figure 2.1). First unmatched input sends request to every output for which it has buffered cell. If unmatched output receives any request, it chooses one randomly to grant. The outputs notify each input whether its request was granted. Finally if an input receives some grants, it chooses one to accept and notifies that output. It's possible that some inputs and outputs remain unmatched. In this case the algorithm runs another iteration excluding operations with previously matched inputs. The explicit schedule is built for each input-output pairings for each slot in a frame. Scheduler can be extended to allocate resources fairly when network is overloaded. Finally, distributed calculations make the system scalable.

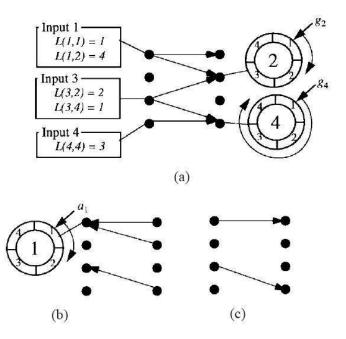

iSLIP algorithm [49]. iSlip algorithm is based on PIM, with the difference that it uses

Figure 2.1: Parallel Iterative Matching: one iteration

rotating priority ("round-robin") arbitration to schedule each active input and output. This fact improves performance, so for uniform traffic in can achieve 100% throughput with single iteration. In fact iSLIP is similar to round-robin matching algorithm with the difference that its not moving grant pointers unless grant is accepted. The operational idea is represented in Figure 2.2. It was found in [49] that for  $N \times N$  switch it takes about  $log_2N$  iterations to converge. It has high throughput for uniform traffic. The algorithm is simple and for small switches arbiter can be placed on a single switch. For N > 1000 ports switch will have large computation overhead, and might not be highly scalable.

Figure 2.2: Representation of iSLIP matching algorithm

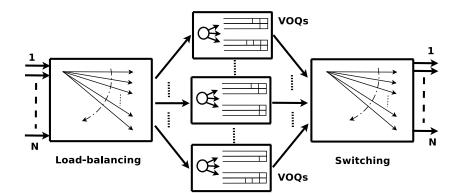

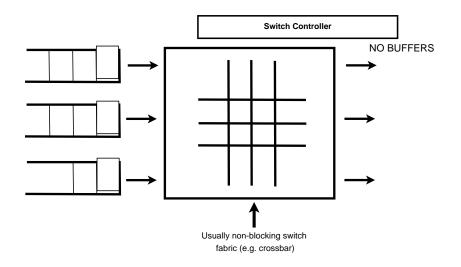

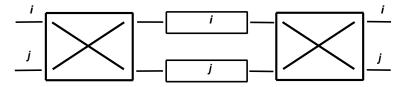

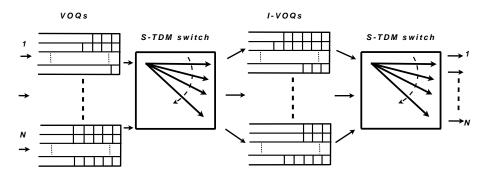

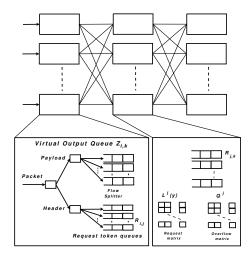

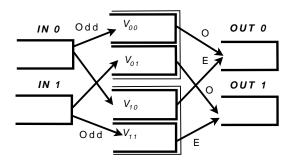

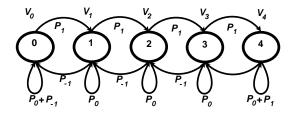

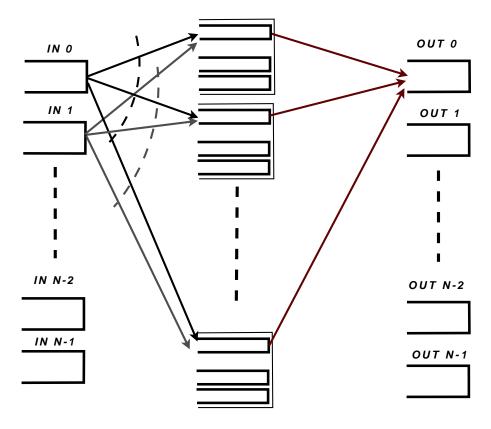

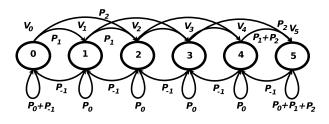

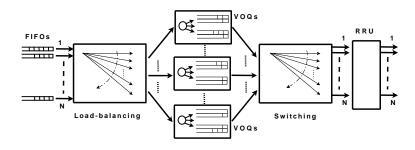

Load-Balancing switching architecture [17, 18]. The architecture is shown in Figure 2.3. It's represented as a stage of buffers positioned in between of two identical crossbar switches. Each line card buffer at an intermediate input in the central stage is partitioned into N separate First-In-First-Out queues, one for each output. The authors of the basic scheme assume the packets of the switch to be of the same size, they call them simply packets [17, 40]. Each linecard inside the switch is synchronized and time

Figure 2.3: The basic LB switch

slotted. This implies that the only one cell can arrive and depart switch during the time slot. Finally each linecard is able to support strictly equal rate flows.

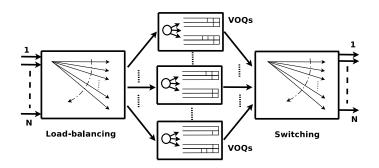

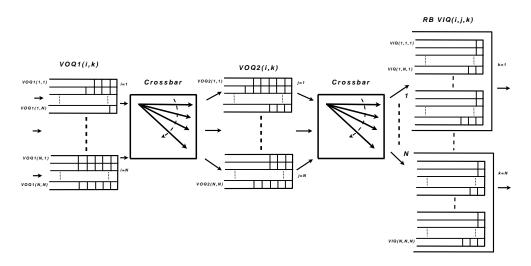

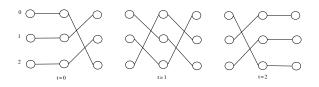

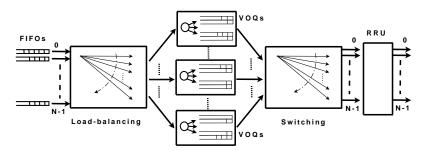

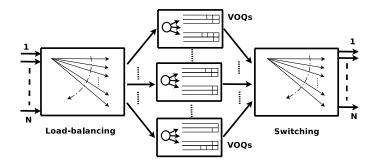

The operational idea behind the distributed  $N \times N$  size architecture is to load-balance or spread uniformly the cells from the input along the VOQs of central buffering stage. Since every component is synchronized, input crossbar periodically interconnect each input to independent buffering units at the central stage. There, the cells positioned in the corresponding to the output port number VOQ. Later on, the VOQ will be served by the second crossbar switch to the output. Input and output crossbars configured similarly with the periodic round-robin connection pattern, linking input, central and output stages. The configuration is not based in the occupancy of the queues, both switching stages walk through a fixed sequence of configurations.

The basic LB switch is promised to be highly scalable. Due to predefined properties it should have a 100% throughput for a broad class of arrival admissible traffic (any traffic distributed uniformly between outputs) even without centralized scheduler. The basic scheme also promises to provide a low average delay even under heavy load and bursty traffic (mathematical representation can be found in [17, 18]). Absence of centralized control mechanism greatly reducing hardware complexity of the switch which makes it easier to implement. Therefore, this architecture was considered as a main candidate for our detailed investigation for the future.

#### 2.1.2 Distributed designs with non-deterministic routes

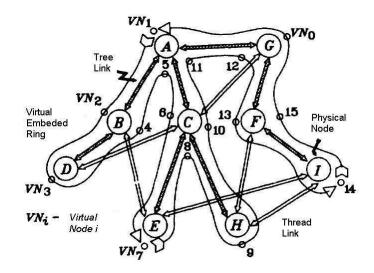

MetaNet convergence routing [54,55]. The structure and operational ideas of MetaNet were first represented in [54]. It is a scalable local area network with an arbitrary topology. The principles of MetaNet are derived from two primitives. The first one refers to exchange of in-band hardware control signals in the network. Another property stands for virtual rings (VR) embedding (Rings and Thread links). These mechanisms are used to linearize the arbitrary topology network for provision of control and global order. Each VR can be constructed according to bidirectional buffer insertion or slotted ring [21].

The spatial reuse provides the ability to concurrently transmit over distinct segments of the ring. Hardware control signals are used to enable independent control functions in the network. Packets in the MetaNet can make short-cuts toward it destination (see Figure 2.4) in order to decrease routing distance. Another possibility is to make jumps on threads. Due to dynamic convergence routing *MetaNet has no packet loss and capable of supporting real time traffic*.

Figure 2.4: Tree embedded ring; short-cut  $(VN_2 - VN_4)$  and jump (C - G)

Manhattan street network [48]. The Manhattan Street Network (MSN) [48] is a self-routing regular topology, originally proposed for local and metropolitan area network applications. An MSN is characterized as a two-connected regular mesh with the nodes connected as rows and columns. Each node consists of a  $2 \times 2$  crossbar switch that connects incoming links to outgoing links. The Clockwork Routing Scheme is a time-slotted system that enhances the MSN. It's includes a simple routing mechanism employed at intermediate nodes that prevents resource contentions, requires no re-sequencing of packets at the destination node and has comparable throughput to conventional routing schemes.

**Deflection or "hot-potato" routing** [8]. The nodes of Hot-potato routing network almost don't have any buffers to store packets in before they are moved on to their final destination. The single input buffer routers are used for operation. Each packet is constantly transferred until it reaches its final destination. The link bandwidth can support maximum one packet which is bounced around like a "hot potato," sometimes moving further away from its destination because it has to keep moving through the network [8]. This is the contrast to the "store and forward" routing where the network allows temporary storage at intermediate locations. The use of input buffer switch for Hot-potato routing is depicted in Figure 2.5.

Figure 2.5: Use of single input buffer switch for Hot-potato, MSN and MetaNet routing

#### 2.1.3 Time-Driven switching

Time-Driven switching [7]. In Fractional lambda Switching  $(F\lambda S)$ , a concept of common time reference (CTR) using UTC (coordinated universal time) is introduced [7]. A UTC second is partitioned into a number of time-frames. Time-frames are switched at every  $F\lambda S$  node with reference to the global CTR. A group of k time-frames forms a timecycle; l continuous time-cycles are grouped into a super cycle. To enable  $F\lambda S$ , time-frames are aligned at the inputs of every  $F\lambda S$  switch before being switched. After alignment, the delay between pair of adjacent switch nodes is an integer number of time-frames. The  $F\lambda S$ , using a global time scheduler, controlling occupancy of time frames. That helps to make provisioning for the future packet transmissions. The architecture reduces packet overhead processing, make usefully bandwidth allocation and efficiently support real-time services.

### 2.2 The Load-Balancing Switching Architecture

In the previous section, a great deal of attention was given to the distributed switching systems as well as to some routers using distributed control. The property to scale is considered to be the central focusing reason for this thesis. In particular, we paid a great amount of interest to the newly proposed LB switching structure. In the above section, we presented some basic knowledge related to the architectural operation principles and assumptions.

In the following section, we will present into details the assumptions and promises given to the initial architecture. We continue with operational principles of the system and short overview of open issues. Further, the detailed analysis of scalability and missequencing problems will be done. In particular, we will analyze scalability of more

Figure 2.6: LB switch with single-stage buffering

complex switches with implemented feedback exchange links and which, correspondingly, require extra computation and communication overheads for proper functioning.

#### 2.2.1 The architecture, assumptions and open issues

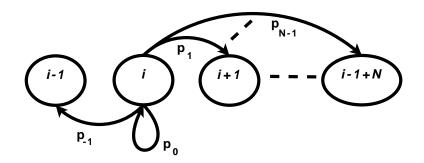

The basic single-stage buffering LB switch is shown in Figure 2.6 and consists of sets of buffers that are positioned in between of two identical crossbar switches [17, 40]. Each crossbar operates through similar predefined interconnection pattern in time according to the following rule:

$$j = (i+t) \mod N,\tag{2.1}$$

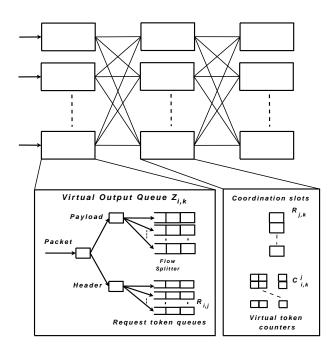

where N is the number of ports in the switch, i is an input(intermediate input at the central stage) number which is interconnected with intermediate input at the central stage (output). Time inside the switch is slotted and each stage assumed to be synchronized with other stages. The transmission of a packet (or a cell) between the stages could be done only in the boundaries of a time slot, i.e., only one packet during each time slot can arrive or depart. Each buffer in the central stage is organized as a set of N queues in a way that there is one queue (VOQ) associated with each output.

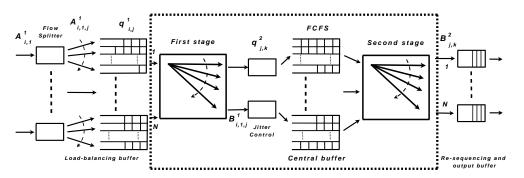

The operating idea behind the N-by-N switch size with a single-stage buffering architecture [17] is to load-balance packets from the inputs along the VOQs of the central buffering stage. Then, the packets are sent to the destination output ports. Arriving packets are switched instantly and there are no buffers inside the crossbars [17, 18].

The main purpose of this section is to highlight the initial LB switch features and to provide the proper background knowledge for the comparative analysis in this chapter further on.

Assumptions. Concerned researchers, such as [16–18, 39, 40] have assumed that all of the LB switch packets are of the same size and they simply call them *packets*. Although in the real Internet world packets have variable length, yet these assumptions have been

idealized and several studies were built upon.

With this thesis, we will be calling packets of the same size as *cells* and, we assume them to be immediate multipliers of the variable size packets. For LB switch support of variable size packets the multi-stage buffering scheme can be used. Usually, input stage buffers are constructed in the similar manner like the central stage VOQs, in order the Head-of-Line blocking to be avoided [18,40]. Another significant statement is relevant to line card synchronization. For each line card the common slotted time is used. Indeed, this assumption implies that the only one cell can arrive and depart switch during the time slot. Finally, each line card is able to support strictly equal rate flows. As one of the major assumptions to permit achievement of high throughput [39] for the initial single/multi-stage LB switch is traffic **admissibility**. Precise definition of this traffic type can be found in the section regarding *input traffic matrixes*.

The listed above fundamental assumptions can be found in each further work regarding LB switching. Definitely, recent schemes can use some specific assumptions due to their complexity (like symmetric interconnection pattern for crossbars); if there any of them will be found, they will be mentioned in the corresponding part.