# Coupling of Photonic Waveguides to Integrated Detectors Using 3D Inverse Tapering

Martino Bernard, Luca Gemma, Davide Brunelli, Senior Member, IEEE, Giovanni Paternoster, and Mher Ghulinyan

Abstract—We report on the design, fabrication, and characterization of a Silicon Nitride (SiN)-based integrated photonic chip in which the dielectric waveguides are coupled to photodetectors integrated homogeneously into the Silicon substrate. The photonic-electronic coupling was realized by a 3D inverse tapering of SiN waveguides. The novelty of our approach consists in tapering the waveguide in the vertical direction by means of an engineered wet chemical etching. This allows for a smooth transition from a full-height to an arbitrarily thin waveguide thickness at the detector location, expanding adiabatically the optical mode towards the latter. The measured chips showed a responsivity  $R\approx 109~\mu\text{A/mW}$  and a corresponding quantum efficiency of 16% at an excitation wavelength of 850 nm. Our technological solution offers a versatile method for a top-down monolithic integration of lightwave circuitries with substrate-located photon sensing devices.

Index Terms—Optical waveguides, photodetectors, photonic integrated circuits, silicon nitride, silicon photonics.

# I. INTRODUCTION

N RECENT years Photonic Integrated Circuits (PIC) experienced enormous growth [1]–[3]. By sharing a large common basis with the mature semiconductor technology, silicon and silicon nitride materials are used to fabricate photonic devices within CMOS facilities, permitting the development of PICs in well-established fabrication plants.

Integration of PICs with photon detectors requires a coupling scheme to transfer the optical power from the waveguide to the detector region. Recently, several strategies have been developed to couple photonic and electronic components for example with SiGe detectors [4] mainly in SiN, SOI and SIN/SOI platforms, as summarized In Table I.

This has become an important topic, especially to foster emerging quantum technologies where the coupling efficiencies with external detectors hampers the development of quantum

Manuscript received 23 February 2022; revised 2 July 2022; accepted 4 July 2022. Date of publication 12 July 2022; date of current version 16 September 2022. This work was supported in part by the European Union's Horizon 2020 research and innovation programme under Grant 777222 under Project: ATTRACT INPEQuT and in part by the EPIQUS under Grant 899368. (Corresponding author: Martino Bernard.)

Martino Bernard, Giovanni Paternoster, and Mher Ghulinyan are with the Centre for Sensors and Devices, Fondazione Bruno Kessler, I-38123 Povo, Italy (e-mail: bernard@fbk.eu; paternoster@fbk.eu; ghulinyan@fbk.eu).

Luca Gemma and Davide Brunelli are with the Department of Industrial Engineering, University of Trento, I-38123 Povo, Italy (e-mail: luca.gemma@unitn.it; davide.brunelli@unitn.it).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JLT.2022.3190041.

Digital Object Identifier 10.1109/JLT.2022.3190041

TABLE I PERFORMANCE COMPARISON

| Measured Responsivity |                                      |         |

|-----------------------|--------------------------------------|---------|

| Work                  | active layer thickness [ $\mu$ m]    | R [A/W] |

| This work             | 3                                    | 0.11    |

| [5]                   | 10                                   | 0.3     |

| [6]                   | other (polysi) 0.15                  | 0.8     |

| [7]                   | other (SOI) 0.22                     | 0.44    |

| [8]                   | other (SOI) 0.22                     | 0.32    |

| [9]                   | other (SOI) 0.25                     | 0.74    |

| [10]                  | other (transf. SOI) 0.22             | 0.19    |

| [11]                  | other (SOI, $\lambda = 685$ nm) 0.25 | 0.83    |

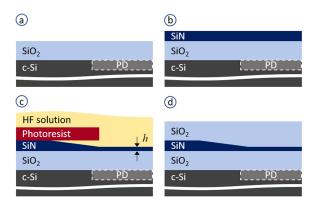

Fig. 1. The sketch of the fabrication process to realize wedge profiles in photonic waveguides. (a) The Si substrate, in which the photodetector devices are already realized, is covered by a thick  $\mathrm{SiO}_2$  cladding, (b) followed by the deposition of the waveguiding  $\mathrm{SiN}$  film. (c) The photoresist patterned  $\mathrm{SiN}$  film is etched in a buffered HF solution to realize a wedge profile. The thickness h of the etched  $\mathrm{SiN}$  film can be controlled via the etch duration. (d) The 3D-shaped PIC layer is covered by an  $\mathrm{SiO}_2$  top cladding.

integrated photonic circuits, and thus research toward integrated solutions is thriving [12]–[15].

This work demonstrates a novel approach to inverse tapering which enables the coupling of SiN waveguide to a Si photodetector integrated in the substrate.

The conventional approach for the realization of an inverse tapering consists in reducing the waveguide width during the pattern definition stage. While this option does not require additional fabrication steps, it is often challenging to reduce the waveguide to an arbitrarily small width without incurring in lithographic limits on critical dimensions. Here, we exploit a chemical wet-etching process to reduce locally the cross-section of the waveguide in the vertical direction (Fig. 1). This, combined with conventional lateral tapering, enables a complete

3D inverse tapering that allows the waveguide losses towards the substrate to be locally enhanced in the region where the photodetector is located. Our approach is largely independent on the lithographic constraints on the waveguide. The fabricated devices show up to 16% quantum efficiency at NIR wavelengths, subject to large improvements upon further optimization of the fabrication process.

The paper is structured as follows: in Section II, we describe the device concept and simulations used to design it. Section III illustrates the fabrication process. In Section IV, the optical and electro-optical characterization of the device are discussed. Finally, Section V summarizes the results and draws conclusions.

# II. NUMERICAL SIMULATIONS

Our approach to waveguide-detector coupling exploits the mode expansion by inverse tapering which allows the optical mode to leak efficiently into the substrate at the detector position. This can be achieved by tailoring the waveguide dimensions from a large cross-section to a weakly guiding small-core one by reducing the thickness of the waveguiding layer, as sketched in Fig. 1(d). The technique used for a shallow-angled wedge formation on thin films is used to shape photonic structures in the vertical dimension, allowing the creation of a smooth transition between two regions in the same photonic layer having different thicknesses [16]–[18]. Such transition in the vertical direction can be eventually paired with an in-plane tapering by using standard lithographic techniques to create a complete 3D tapering of the waveguide.

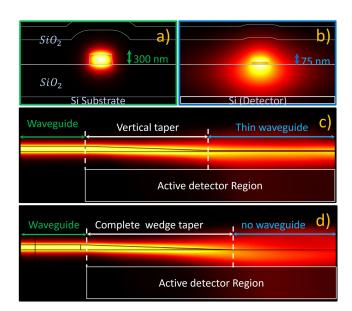

The device under study consists of an electronic-photonic integrated circuit structured as follows. The epitaxial Silicon substrate hosts the photodetectors, formed by ion-implanted p-njunctions. The photonic layer is formed on top of the substrate and consists of single-mode waveguides which allow for guided mode propagation without losses towards the substrate. At the location of the p-n junctions, the light is transferred from the waveguide to the underlaying photodetector via 3D inverse tapering of the waveguide. While our numerical simulations are performed for SiN-based single-mode channel waveguides, the method described here is general and can be extended to other photonic material platforms and waveguide geometries. Numerical simulations, performed using the Finite Elements Method (FEM), allow to obtain the geometrical parameters and the modal characteristics of the waveguides. In particular, the channel waveguides of 300 nm height and 700 nm on top of  $\sim 1~\mu \mathrm{m~SiO_2}$  bottom cladding allow for single mode propagation with low loss towards the Si substrate (Fig. 2(a)). Fig. 2(b) shows the small core region after the tapering, where most of the mode energy is squeezed out of the core of the waveguide down into the substrate-integrated photodetector with a corresponding loss of 2400 dB/cm. In this case the waveguide width and the height are reduced to 500 nm and to 75 nm, respectively. Fig. 2(c) shows the distribution of the electromagnetic field intensity in the transverse cross-section of the waveguide. In this case, light propagates from the thick waveguide on the left towards the small waveguide on the right, passing through the wedge

Fig. 2. Numerical simulations of electromagnetic field intensity in (a) the PIC region, where the waveguide is large enough to contain the field, (b) at the detector region, where the reduced waveguide height does delocalizes the mode and leaks into the substrate. (c) A side-view of the waveguide. The waveguide is 300 nm thick in the PIC (left), and is progressively thinned in the vertical taper region via wet-etching (center). Finally, the waveguide with a reduced height of 74 nm allows the mode to leak energy into the underlaying photodetector (right). (d) The wedge-terminated waveguide does not scatter towards the top due to cladding confinement while it couples to the substrate at the bottom.

transition. Underneath the thin portion of the waveguide, the light is collected within the active region of a photodiode. The complete inverse tapering case, where the waveguide thickness is brought down to zero, is shown in Fig. 2(d). Here, above the photodetector, the light is essentially confined within the top  $SiO_2$  cladding and the highly absorbing Si substrate.

## III. DEVICE FABRICATION

The devices were fabricated starting from 6-inch epitaxial Si substrates in which, first, the photodetectors were realized by ion implantation of Phosphorous and Boron to form the p-njunctions. The photodetectors have an elongated shape following the waveguide trace in order to permit an efficient collection of the evanescent light field within an extended region. Fig. 3(a) shows the CAD layout of the detector region, where the Phosphorous and Boron doping regions are visible highlighted in red and blue, respectively. On top of the Si substrate, a 1050 nm thick bottom SiO<sub>2</sub> cladding layer of is deposited in order to isolate the PIC from the substrate (see the sketch in Fig. 1(a)). Next, the wafer is covered with a 7 nm thin film of Si<sub>3</sub>N<sub>4</sub> via Low-pressure Chemical Vapour Deposition (LPCVD) to realize an etch-stop layer, the utility of which will be explained in the following. Then, a SiN film of 300 nm is deposited via Low-frequency (380 kHz) Plasma-enhanced Chemical Vapour Deposition (PECVD) to form the the photonic device layer (Fig. 1(b)).

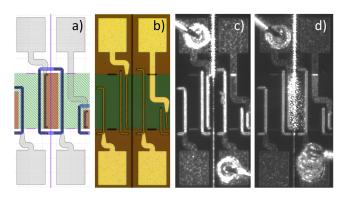

Fig. 3. (a) The CAD layout of the detector showing the active p- (red) and n-doped (blue) regions, (purple) waveguide and (grey) pads. The green area represents the region where the waveguides height is reduced. (b) An optical micrograph of the fabricated device. (c) Light coupling from the thin waveguide to the detector. (d) Light coupling from a wedge-terminated waveguide to the detector.

At this stage, the definition of the vertical tapering is realized by opening a window in the photoresist at the location of photodetectors and wet etcing the SiN film in a buffered HF solution (BHF) (Fig. 1(c)). While the wet etching consumes slowly the SiN film isotropically, at the same time, the BHF erodes progressively the interface between the photoresist film and the SiN layer, promoting an additional etching front at the photoresist-SiN interface. For appropriate combinations of the etched material, the adhesion promoter and the curing process of the photoresist, the etching speed along the photoresist-SiN interface can be made faster than the isotropic etching rate of the SiN film itself. This situation generates a triangular-shaped etching front, producing the wedge-shaped transition shown in Fig. 1(c). We have produced different wafers in which the SiN film was either thinned down to 75 nm or eliminated completely to form a complete inverse tapering. The latter situation can be achieved precisely due to the presence of the etch-stop Si<sub>3</sub>N<sub>4</sub> film which prevents ethcing of the bottom SiO<sub>2</sub> cladding. The procedure, physics, and mathematical description of the wet-etching process are described in more detail in [19], [20].

After the realization of the wedge tapering, the waveguides were patterned with i-line stepper lithography and reactive ion etching (RIE), shown as purple lines in Fig. 3(a). Then the waveguides were treated thermally at 975 °C for 1 h in an N  $_2$  atmosphere to release the residual hydrogen from the PECVD film, and to activate the doping in the epitaxial substrate. Next, the wafer was covered with another 7 nm thick LPCVD  $\rm Si_3N_4$ , followed by a deposition of 1  $\mu m$  thick Tetraethylorthosilicate (TEOS)  $\rm SiO_2$  which acts as a top cladding (Fig. 1(d)).

The wafer was then patterned with stepper lithography to realize vias through the top cladding, the intermediate  $\mathrm{Si}_3\mathrm{N}_4$  film and the bottom  $\mathrm{SiO}_2$  to allow the deposition of metal contacts in the doped regions. The vias were formed via Deep RIE. Additional non-contacting vias were etched in various regions of the chips close to the waveguides and the detectors, which were later filled with Aluminium to form barriers for stray light travelling in the oxide layers. The wafer was then

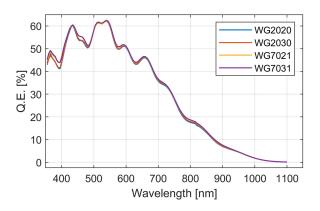

Fig. 4. The quantum efficiency of the diodes exposed to a normal illumination from an external spectral source. The spectral features with  $\approx 50$  nm of period are due to thin-film interference of the cladding covering the photodiode.

covered with a 1.2  $\mu$ m thick layer of Al-1% Si alloy, sputtered at 200 °C, in order to contact the p-n junction. The metallic film was patterned into wires and contact pads via lithography and defined with RIE. Fig. 3(b) shows an optical micrograph of the realized device. It's worth noting the elongated shape of the Aluminium vias that form a mirror-cage in the cladding all around the photodetector region except in the proximity to the waveguides. Finally, the diced chips were wire bonded to PCB boards for optical/electrical characterization. Fig. 3(c) and Fig. 3(d) show two devices with bonded electronics, with thinned waveguide and complete inverse tapering, respectively. The light here is injected into the waveguide from the top part of the figure towards the bottom.

## IV. MEASUREMENTS

First, the photodiodes were characterized for normal incidence responsivity, that is, from external illumination from an external source directly impinging on the detector surface. The current at -1 V bias, generated by excitation from a spectral lamp, was measured and power-normalized with a calibrated detector. Fig. 4 shows the spectral responsivity to normal incidence of four photodiodes. The responsivity remains substantially identical for the different devices, with spectral features with a period of  $\approx 50$  nm due to thin-film interference of the cladding film on top of the photodiode. We have investigated the waveguide-coupled quantum efficiency (Q.E.) at a wavelength of 850 nm, where the PIC is expected to operate. However, the responsivity of the silicon detectors is higher at shorter wavelengths, and thus the method is more efficient for devices operating with visible light.

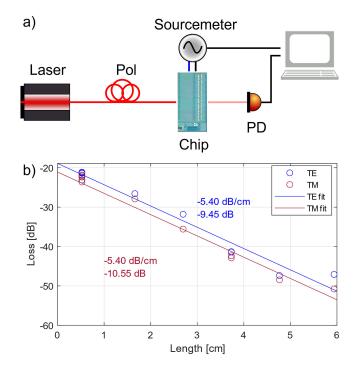

Next, the devices were tested for excitation from the integrated waveguide by using the setup shown in Fig. 5(a). Light from a laser diode emitting at 850 nm is injected into the waveguide using a tapered lensed fiber. The light travels in the waveguide until it reaches the region above the detector. Here, the waveguide geometry is varied to expand the mode profile into the underneath detector, where a photocurrent is generated and measured with the sourcemeter. After the detector region, the

Fig. 5. (a) Experimental setup used to measure the responsivity of the diodes from waveguide excitation. The light of a laser diode (Thorlabs LP850-SF80) is injected into the chip via tapered lensed fibers. The light polarization is set by an in-fiber polarization control stage. The light travels through the waveguide and is coupled to the integrated photodetector. The photocurrent at -1 V bias is measured by a sourcemeter (Ketheley 2450), while any residual light in the waveguide is collected with another tapered fiber and sent to an external Si detector (PDA100A2). (b) Experimental characterization of the samples optical losses. The power transmission of waveguides of different lengths is measured and fitted via a Beer-Lambert law to estimate insertion and propagation losses for the chips.

waveguide cross-section is tapered back to its original dimensions. The residual light is then collected at the output facet with another tapered lensed fiber and sent to an external Si detector. In order to estimate the Q.E. of the photodetectors with respect to the PIC we have estimated the light power in the waveguide right before the coupling region with the photodetector. This estimation is realized by subtracting from the calibrated 5 mW source the optical losses that occur in the chip before the detector. Optical losses are mostly due to the insertion loss at the input fiber-to-waveguide coupling interface and the propagation loss in the waveguide from the edge of the sample to the detector region.

Both insertion and propagation losses were estimated via cut-back method on a twin chip, realized on the same wafer next to the one hosting the photodetectors. On the testing chip, spiral waveguide structures with lengths from 0.5 cm to 6 cm were present, allowing for a loss estimation through Beer-Lambert law fitting of the transmission data. Fig. 5(b) represents the propagation loss data samples for both transverse-electric (TE, blue) and transverse-magnetic (TM, red) input polarizations. While TE polarization exhibits slightly lower propagation loss, the devices are expected to show better operation in TM polarization, where the coupling towards the substrate is higher, and hence the generated photocurrent is larger. Once the propagation

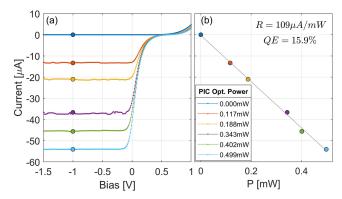

Fig. 6. (a) IV-curves with varying input optical power and (b) the responsivity of the photodiode coupled to a thinned waveguide.

losses are estimated, the detector responsivity is measured with the setup shown in Fig. 5(a). This time, variable optical power is injected into the optical waveguides coupled to the detectors. The optical power before the detector,  $P_{\rm in}$ , is calculated by subtracting insertion and propagation losses inside the chip from the laser power, which is monitored with a calibrated power-meter (S120VC). For each level of input optical power an IV-curve is measured on the detector, as shown in Fig. 6(a). In Fig. 6(b) we plot the generated photocurrent  $I_{ph}$  at -1 V bias as a function of the input optical power  $P_{\mathrm{in}}$ . From fitting the data with a linear regression, the responsivity  $R = I_{\rm ph}/P_{\rm in}$  of the detector can be estimated, which in our case is 0.109 A/W. The quantum efficiency of our devices has been estimated as  $Q.E. = I_{\rm ph}/P_{\rm in} \times h\nu/e$  where h is the Plank constant,  $\nu$  is the frequency of the photons and e is the elementary charge. From the measurements, the Q.E. of the device resulted as high as 15.9%, which is very close to the predicted 16.7% from FEM simulations.

We have also characterized chips with complete inverse tapering (Fig. 2(d)). Here, the light diffuses into the  ${\rm SiO_2}$  cladding, which can be appreciated from the optical image shown in Fig. 3(d). The photodetector still absorbs the light trapped in the cladding, but at a slower rate. In this case, an efficient coupling in the active region is ensured by caging the light with deep trenches filled with metal which act as mirrors. Thanks to the lateral confinement provided by the metal cage, these devices achieve a Q.E. of 15.4%, similar to that of the thinned waveguides.

We note, that the measured responsivities are comparable with the state-of-the-art R's in waveguide-integrated photodetectors, which are typically of the order of 0.3 A/W [5]–[7]. Here, the lower values of R can be explained by the fact that the absorbance value of the realized devices is mostly limited by the thickness of the epitaxial layer, which is 3  $\mu \rm m$  in our devices. The epitaxial layer, determines the detector's active volume where the photogenerated electron-hole pairs are collected. Even though the light couples to the substrate from a waveguide parallel to the surface, Snell refraction bends the light to about 60  $^{\circ}$  with respect to the SiN/Si interface, thus reducing the optical path within the active layer to approximately 3  $\mu \rm m$   $/sin(60~^{\circ})\approx 3.5~\mu \rm m$ . In fact, in Ref. [5], which uses a 10  $\mu \rm m$  epitaxial Si, an  $R\approx 0.3$  A/W has been demonstrated. Nevertheless, as in the case for the devices

described in [5], this issue can be mitigated with the use of thicker epitaxial layers or with back-side reflector strategies.

### V. CONCLUSION

The geometries we tested for substrate-coupling of the light at the end of a PIC show promising results to be used in integrated devices fabricated with optical lithography, especially where monitor photodiodes are required. Our coupling strategy provides a simple reliable coupling method which is broadband, resolution-insensitive and robuts to fabrication toleracies. We believe that our method could provide an excellent alternative to grating couplers that, being essentially resonant structures, are bandwidth-limited and sensitive to fabrication tolerances. In particular, the vanishing-waveguide variation is efficient for short-wavelength applications where a thick oxide impedes the evanescent coupling and the definition of a grating coupler is particularly challenging. With respect to other approaches developed for waveguide-photodetector coupling, the technology described in this paper permits an independent development of arbitrary electronics within the epitaxial Si substrate, followed by an integration of arbitrary PIC architecture on top of the substrate. The future perspective is to use this technology to couple SiN photonic circuitries with single-photon avalanche diodes [21] in order to make a step forward towards the development of VIS-NIR operating quantum photonic platform in silicon.

# ACKNOWLEDGMENT

We acknowledge the support of the MNF Laboratory staff of FBK during sample fabrication. We wish to thank Lucio Pancheri and Georg Pucker for useful discussion. We acknowledge financial support from the Autonomous Province of Trento, under the initiative "Quantum at Trento - Q@TN", projects Q-PIXPAD and CoSiQuP.

### REFERENCES

- [1] L. A. Coldren, S. W. Corzine, and M. L. Mashanovitch, *Diode Lasers and Photonic Integrated Circuits*. Hoboken, NJ, USA: Wiley, 2012.

- [2] T. L. Koch and U. Koren, "Semiconductor photonic integrated circuits," IEEE J. Quantum Electron., vol. 27, no. 3, pp. 641–653, Mar. 1991.

- [3] R. Nagarajan et al., "Large-scale photonic integrated circuits," *IEEE J. Sel. Topics Quantum Electron.*, vol. 11, no. 1, pp. 50–65, Jan./Feb. 2005.

- [4] D. Benedikovic et al., "Silicon-germanium receivers for short-wave-infrared optoelectronics and communications," *Nanophotonics*, vol. 10, no. 3, pp. 1059–1079, 2021.

- [5] M. Bernard et al., "Top-down convergence of near-infrared photonics with silicon substrate-integrated electronics," *Optica*, vol. 8, no. 11, pp. 1363–1364, 2021.

- [6] A. Samusenko et al., "Integrated silicon photodetector for lab-on-chip sensor platform," in *Proc. IEEE 28th AISEM Annu. Conf.*, 2015, pp. 1–4.

- [7] A. Chatterjee, S. Sam, S. K. Sikdar, and S. K. Selvaraja, "High-speed waveguide integrated silicon photodetector on a Sin-Soi platform for short reach datacom," *Opt. Lett.*, vol. 44, no. 7, pp. 1682–1685, 2019.

- [8] M. M. P. Fard, C. Williams, G. Cowan, and O. Liboiron-Ladouceur, "High-speed grating-assisted all-silicon photodetectors for 850 nm applications," *Opt. Exp.*, vol. 25, no. 5, pp. 5107–5118, Feb. 2017. [Online]. Available: https://opg.optica.org/oe/abstract.cfm?uri=oe-25-5-5107

- [9] K. Ohira et al., "On-chip optical interconnection by using integrated III-V laser diode and photodetector with silicon waveguide," Opt. Exp., vol. 18, no. 15, pp. 15440–15447, Jul. 2010. [Online]. Available: http://opg.optica.org/oe/abstract.cfm?URI=oe-18-15-15440

- [10] S. Cuyvers et al., "Heterogeneous integration of Si photodiodes on silicon nitride for near-visible light detection," *Opt. Lett.*, vol. 47, no. 4, pp. 937–940, Feb. 2022. [Online]. Available: https://opg.optica.org/ol/abstract.cfm?uri=ol-47-4-937

- [11] S. Yanikgonul et al., "Integrated avalanche photodetectors for visible light," *Nature Commun.*, vol. 12, no. 1, pp. 1–8, 2021.

- [12] T. Gerrits et al., "On-chip, photon-number-resolving, telecommunication-band detectors for scalable photonic information processing," *Phys. Rev. A*, vol. 84, no. 6, 2011, Art. no. 060301.

- [13] C. Schuck, X. Guo, L. Fan, X. Ma, M. Poot, and H. X. Tang, "Quantum interference in heterogeneous superconducting-photonic circuits on a silicon chip," *Nature Commun.*, vol. 7, no. 1, 2016, Art. no. 10352.

- [14] S. Ferrari, C. Schuck, and W. Pernice, "Waveguide-integrated superconducting nanowire single-photon detectors," *Nanophotonics*, vol. 7, no. 11, pp. 1725–1758, 2018.

- [15] S. Gyger et al., "Reconfigurable photonics with on-chip single-photon detectors," *Nature Commun.*, vol. 12, no. 1, 2021, Art. no. 1408.

- [16] F. Ramiro-Manzano, N. Prtljaga, L. Pavesi, G. Pucker, and M. Ghulinyan, "A fully integrated high-Q whispering-gallery wedge resonator," *Opt. Exp.*, vol. 20, no. 20, pp. 22934–22942, 2012.

- [17] H. Lee et al., "Chemically etched ultrahigh-q wedge-resonator on a silicon chip," *Nature Photon.*, vol. 6, no. 6, pp. 369–373, 2012.

- [18] X. Zhang, M. Harrison, A. Harker, and A. M. Armani, "Serpentine low loss trapezoidal silica waveguides on silicon," *Opt. Exp.*, vol. 20, no. 20, pp. 22298–22307, 2012.

- [19] G. Parisi, S. Haszko, and G. Rozgonyi, "Tapered windows in SiO<sub>2</sub>: The effect of nh 4 F: HF dilution and etching temperature," *J. Electrochem. Soc.*, vol. 124, no. 6, 1977, Art. no. 917.

- [20] M. Ghulinyan, M. Bernard, R. Bartali, and G. Pucker, "Formation of mach angle profiles during wet etching of silica and silicon nitride materials," *Appl. Surf. Sci.*, vol. 359, pp. 679–686, 2015.

- [21] F. Acerbi, G. Paternoster, A. Gola, N. Zorzi, and C. Piemonte, "Silicon photomultipliers and single-photon avalanche diodes with enhanced NIR detection efficiency at FBK," Nucl. Instrum. Methods Phys. Res. Secti. A: Accel., Spectrometers, Detect. Assoc. Equip., vol. 912, pp. 309–314, 2018.

Martino Bernard received the B.S., M.S., and the Ph.D. degrees from the University of Trento, Trento, Italy, in 2011, 2013, and 2017, respectively. He is currently a Researcher with the Centre for Sensors and Devices Fondazione Bruno Kessler, Trento, Italy. He has authored or coauthored more than 20 papers. His research interests include photonic integrated circuits, with particular focus of ring resonators, and photonic-electronic integration for the Quantum technologies. His current research interests include integrated & quantum optics unit, focusses on the integration of photonic circuits with control electronics and detectors.

**Luca Gemma** received the master's degree in mechatronic engineering from the University of Trento, Trento, Italy. He is currently working toward the Ph.D. degree in mechatronic engineering with Fondazione Bruno Kessler, Trento, Italy. He has collaborated with Fondazione Bruno Kessler, where he is designing an electronic architecture for a quantum chip. His research interests include deep learning and embedded electronics.

Davide Brunelli (Senior Member, IEEE) received the M.S. (cum laude) and Ph.D. degrees in electrical engineering from the University of Bologna, Bologna, Italy, in 2002 and 2007, respectively. He is currently an Associate Professor of electronics with the Department of Industrial Engineering, University of Trento, Trento, Italy. He has authored or coauthored more than 240 research papers on international conferences and journals in the area of ultra-low-power embedded systems, energy harvesting, and power management of VLSI circuits. His research interests include IoT and distributed lightweight unmanned aerial vehicles UAV, the development of new techniques of energy scavenging for low-power embedded systems, and energy-neutral wearable devices. He was leading industrial cooperation activities with TIM Italia, Rome, Italy, ENI, Rome, Italy, and STMicroelectronics, Geneva, Switzerland. He is an ACM Member.

Giovanni Paternoster received the M.S. degree in applied physics from the University of Pisa, Pisa, Italy and the Ph.D. degree in physics from the University of Trento, Trento, Italy, in 2013. Since 2013, he has been as a Researcher with Micro Nano Facility Unit, Fondazione Bruno Kessler (FBK), Trento, Italy. Since 2022, he coordinates the Detector Technology Group within the "Custom Radiation Sensors" unit. He contributed to the development of the high-density SiPM (HD-SiPM) and LGAD technologies for fast timing with FBK. His research interests include the fabrication process and technology development of silicon radiation sensors, and in particular of silicon photomultipliers and low gain avalanche diodes.

Mher Ghulinyan received the M.S. and Ph.D. degrees from Yerevan State University, Yerevan, Armenia, in 1995 and 1999, respectively. He is currently a Senior Researcher with the Centre for Sensors and Devices with Fondazione Bruno Kessler, Trento, Italy. He has several years of experience in teaching Photonics with the University of Trento, Trento, Italy. He has authored more than 130 research papers and is an Inventor of several patents. His research interests include the field of waveguide and resonator optics, with a particular focus on the technological developments towards integrated silicon-based quantum photonics and heterogeneously integrated active silicon photonics. He is a Senior Member of the Optica (former OSA).